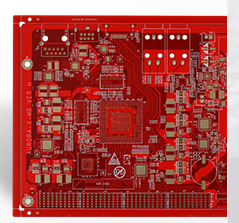

表面貼裝科技中, 混合集成 PCB科技 是開發的新一代電子組裝技術. 表面貼裝科技的廣泛應用促進了電子產品的小型化和多功能化, 為批量生產和低缺陷率生產提供了條件.

1.PCB和IC烘烤

1、PCB使用時間不超過3個月,無潮濕,無需烘烤。 超過3個月後,烘烤時間為4.小時

2、溫度:80-100度; 集成電路:BGA封裝

3.1個月後,必須散裝烘焙24小時,新的散裝包裝至少烘焙8小時。 如果它是一個舊的或拆卸的集成電路,它必須烘烤3天。 溫度:100-110度; QFP/SOP/和其他具有原始真空的封裝集成電路封裝不需要烘焙,而散裝封裝需要烘焙至少8小時,溫度:100-110度

二, PCB貼片

1、錫膏工藝

2、紅膠工藝

3、鉛工藝

4、無鉛工藝

smt加工流程

3、每個組裝編號的PCB元件的類型、型號、標稱值和極性

為了滿足產品裝配圖和時間表或BOM要求(是否應磨合IC),安裝的部件應完好無損。

第四,安裝部件的焊端或焊脚應浸入厚度不小於1/2的焊膏中。

對於一般部件,錫膏擠出量(長度)應小於0.2mm,對於窄間距部件,錫膏擠出量(長度)應小於0.1mm。

5.PCB組件的端部或引脚與接地圖案對齊並居中。

由於回流焊接過程中的自定位效應,元件的放置位置允許有一定的偏差。 允許偏差範圍要求如下:

1、矩形元件:元件寬度方向上的焊端寬度大於焊盤上的1/2; 元件焊接端和焊盤必須在元件的長度方向上重疊; 當存在旋轉偏差時,元件焊接端的寬度必須為焊盤上寬度的1/2或更大。

2、小輪廓電晶體(SOT):允許X、Y、T(旋轉角度)偏差,但引脚(包括脚趾和脚跟)必須全部在焊盤上。

3、小外形集成電路(SOIC):X、Y、T(旋轉角度)允許有安裝偏差,但器件引脚寬度的3/4(包括脚趾和脚跟)必須在墊板上。

4. Quad Flat Package Devices and Ultra Small Package Devices (QFP): It is necessary to ensure that 3/引脚寬度的4%位於焊盤上, X的安裝偏差較小, Y, and T (rotation angle) are allowed. 允許銷的脚趾從墊子上稍微突出一點, 但必須有3個/上銷長度的4 PCB焊盤, 銷的後跟也必須在墊子上.

6、常規貼片資料必須符合IPC-310和IPC-610標準。

PCB表面必須清潔

血液中不得有錫珠或錫渣。

8.PCB測試範圍

檢查指示燈是否亮起,搜索者是否找到IP,測試影像是否正常,電機是否旋轉,測試語音測試語音監控和對講,機器和電腦都必須有聲音,還提供批量生產和低缺陷率生產條件。