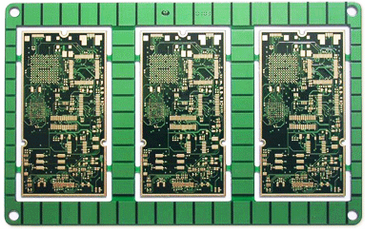

高速DSP系統中PCB板可靠性設計應注意的幾個問題.

1、電源設計

首先需要考慮的是 PCB設計 高速DSP系統的覈心是電源設計. 電源設計中, 以下方法通常用於解决信號完整性問題.

2、考慮電源和接地的去耦

隨著DSP工作頻率的新增,DSP和其他集成電路組件趨向於小型化和密集封裝。 通常,電路設計中會考慮多層板。 建議電源和接地都可以使用專用層,對於多個電源,例如,DSP輸入/輸出電源電壓不同於覈心電源電壓,可以使用兩個不同的電源層。 如果考慮多層板的處理成本,則專用層可用於更多佈線或相對關鍵的電源。 電源的佈線可以與訊號線相同,但線的寬度必須足够。

無論電路板是否有專用的接地層和電源層,都必須在電源和接地之間添加一定且分佈合理的電容器。 為了節省空間和减少通孔的數量,建議使用更多的片式電容器。 晶片電容器可以放置在PCB板的背面,即焊接表面。 片式電容器用寬導線連接到通孔,並通過通孔連接到電源和接地。

3、考慮配電的接線規則

獨立的類比和數位功率層

高速高精度類比元件對數位信號非常敏感。 例如,放大器會放大開關雜訊,使其接近脈衝訊號,囙此電路板的類比和數位部分、功率層通常需要分開。

隔離敏感訊號

一些敏感訊號(如高頻時鐘)對雜訊干擾特別敏感,必須對其採取高級隔離措施。 高頻時鐘(20MHz以上的時鐘或翻轉時間小於5ns的時鐘)必須有地線護送,時鐘線寬應至少為10密耳,護送地線寬度應至少為20密耳。 孔與地面接觸良好,每隔5cm沖孔與地面連接; 時鐘發送側必須與22Î220Î)的阻尼電阻器串聯。 可以避免這些線路帶來的訊號雜訊造成的干擾。

軟硬體抗干擾設計

通常地, 高速DSP應用 系統PCB 單板由用戶根據系統的具體要求進行設計. 由於設計能力和實驗室條件有限, 如果沒有採取完善可靠的抗干擾措施, 一旦工作環境不理想, 電磁干擾會導致DSP程式流混亂. 當DSP的正常工作程式碼無法恢復時, 程式將運行或崩潰, 有些部件甚至可能損壞. 應注意採取相應的抗干擾措施.

硬體抗干擾設計

硬體抗干擾效率高。 當系統複雜度、成本和體積可以容忍時,首選硬體抗干擾設計。 常用的硬體抗干擾科技可歸納為以下幾類:

(1)硬體濾波:RC濾波器可以大大衰减各種高頻干擾訊號。 例如,可以抑制“毛刺”的干擾。

(2)合理接地:合理設計接地系統,對於高速數位和類比電路系統,具有低阻抗、大面積接地層非常重要。 接地層不僅可以為高頻電流提供低阻抗返回路徑,還可以减小EMI和RFI,並對外部干擾具有遮罩作用。 在PCB設計期間,將類比接地與數位接地分開。

(3)遮罩措施:交流電源、高頻電源、强電流設備、電弧產生的電火花會產生電磁波,成為電磁干擾的雜訊源。 金屬外殼可用於包圍上述設備並將其接地。 這對遮罩電磁感應引起的干擾非常有效。

(4)光電隔離:光電隔離器可以有效避免不同電路板之間的相互干擾。 高速光電隔離器通常用於DSP與其他設備(如感測器、開關等)的介面。

軟件抗干擾設計

軟件抗干擾具有硬體抗干擾無法替代的優點。 在DSP應用系統中,還應充分發揮軟件的抗干擾能力,以儘量減少干擾的影響。 下麵給出了幾種有效的軟件抗干擾方法。

(1)數位濾波:類比輸入信號的雜訊可以通過數位濾波消除。 常用的數位濾波科技包括:中值濾波、算術平均濾波等。

(2)設定陷阱:在未使用的程式區域設置引導程式的一部分。 當程式受到干擾並跳轉到此區域時,引導程式將強制將捕獲的程式引導到指定的地址,並使用特殊程式糾正那裡的錯誤程式。 處理。

(3)指令冗餘:在雙位元組指令和3位元組指令之後插入兩個或3個位元組的無操作指令NOP,當DSP系統受到程式跑掉的干擾時,可以防止程式自動進入正確的軌道。

(4)設定看門狗計時:如果失控程式進入“無限迴圈”,則通常使用“看門狗”科技使程式脫離“無限迴圈”。 原理是使用計時器,根據設定的週期生成脈衝。 如果不想產生該脈衝,DSP應在小於設定週期的時間內清除計時器; 但當DSP程式運行時,它不會根據需要清除計時器,計時器生成的脈衝將用作DSP重置訊號,以再次重置和初始化DSP。

4、電磁相容設計

電磁相容性是指電子設備在複雜電磁環境中正常工作的能力。 電磁相容性設計的目的是使電子設備能够抑制各種外部干擾,同時也减少電子設備對其他電子設備的電磁干擾。 在實際PCB板中,或多或少存在電磁干擾現象,即相鄰訊號之間的串擾。 串擾的大小與環路之間的分佈電容和分佈電感有關。 可以採取以下措施來解决訊號之間的相互電磁干擾:

5、選擇合理的導線寬度

瞬態電流對印刷線路的影響主要由印刷線路的電感引起,其電感與印刷線路的長度成正比,與寬度成反比。 囙此,使用短而寬的導線有利於抑制干擾。 時鐘引線和匯流排驅動器的訊號線通常具有較大的瞬態電流,其印製線應盡可能短。 對於分立元件電路,印刷線寬度約為1.5mm,以滿足要求; 對於集成電路,印刷線寬度選擇在0.2mm到1.0mm之間。

採用tic-tac-toe網路佈線結構。

具體方法是在第一層佈線 PCB印製板, 和下一層的垂直佈線.