Die Verkabelung der PCI-Karte ist exquisiter, die durch die Eigenschaften des PCI-Signals bestimmt wird. In der konventionellen Hochfrequenz-Digitaltechnik Leiterplatte Design, Wir bemühen uns immer, Signalreflexion zu vermeiden, Überschuss, Klingeln, und nicht-monotone Phänomene, die durch Impedanzanpassung verursacht werden. Allerdings, PCI-Signale verwenden das Prinzip der Signalreflexion, um physikalisches Signal zu übertragen, um die Signalreflexion sinnvoll zu nutzen und gleichzeitig Nebenwirkungen wie große Überschreitung zu vermeiden, Klingeln und Nichtmonotonie, PCI-SIG hat einige Bestimmungen zur physikalischen Realisierung von Leiterplatten in der PCI-Spezifikation getroffen.

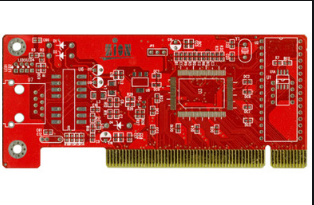

PCI-SIG empfiehlt die Verwendung eines Vierschichtige Leiterplatte Platine für PCI-Karten. Die von PCI-SIG spezifizierte Signalverteilung der PCI-Steckverbinder ist auch für den Komfort der vierlagigen Leiterplattenverkabelung optimiert. PCI-SIG hat auch ein empfohlenes Schema für die Pin-Verteilung von PCI-Controllern erstellt. In der Tat, Hersteller von PCI-Controllern wie AMCC, PLX, und OXFORD haben diese Empfehlung ebenfalls umgesetzt. Unter dieser empfohlenen Pin-Verteilung, zwei Schichten werden verwendet. Die Leiterplatte ist eigentlich sehr bequem für die Verdrahtung, aber wenn die Hardware des PCI-Kartensystems sehr komplex ist und mehrere Power Split Levels erfordert, Es ist besser, eine mehrschichtige Leiterplatte zu haben.

Jedes PCI-Signal auf der PCI-Karte kann nur an eine Last angeschlossen werden (auch nicht an einen Pull-Up-Widerstand). Außer CLK, RST, INTA#~INTD#, JTAG diese Pins, alle Pins vom Kontaktpunkt des goldenen Fingers und der Kartenbuchse zum Lastende dürfen nicht größer als 1.5 Zoll sein; Die Länge des CLK-Signals ist 2,5 +-0,1 Zoll, diese Länge Es ist etwas lang, so dass es in vielen Fällen geroutet werden muss, um die Längenanforderung zu erfüllen. Deshalb sehen Sie oft die Serpentinenspur von CLK auf der PCI-Karte; Für die restlichen Pins gibt es keine besonderen Vorschriften. Bei Verwendung einer mehrschichtigen Leiterplatte sollten die Signalspuren nicht verschiedene Leistungsstufen kreuzen (zumindest sollte sich die Schicht mit dem geteilten Leistungspegel auf der anderen Seite der Leiterplatte befinden), weshalb wir oft sehen, dass alle Goldfinger auf der A-Seite der PCI-Karte auftauchen. Der Grund, warum das Signal oft auf die B-Seite (Komponentenseite) durch ein Loch geht.

Die charakteristische Impedanz jedes PCI-Signals beträgt 60-100 Ohms, und die Lastkapazität darf 10pf nicht überschreiten. Das IO Pad des IC sollte -3,5V Undershoot und +7,1V Signal Overshoot aushalten können. Für PCI-Controller-Hersteller wie AMCC, PLX und OXFORD erfüllt der Controller-IC diese Vorschriften, und Benutzer müssen sie nicht berücksichtigen. Wenn Sie jedoch CPLD/FPGA zur Implementierung des PCI-Controllers verwenden, müssen Sie überlegen, ob das verwendete Modell diesen Vorschriften entspricht. CPLD/FPGA-Hersteller wie Altera und Xilinx werden in ihren Datenhandbüchern klar angeben, ob das CPLD/FPGA mit PCI-Signalspezifikationen kompatibel ist.

Nun ja, Die Verdrahtung der gewöhnlichen 32-Bit 33MHz PCI Karte ist relativ einfach, hauptsächlich, um die Längenanforderungen zu erfüllen. In der Tat, wenn Sie die Verdrahtungsanforderungen nicht strikt befolgen, es wird generell keine Probleme geben, aber abhängig vom Motherboard-Chipsatz, sobald das Problem der Signalkompatibilität auftritt, Das Hardwaredebuggen der PCI-Karte wird die schmerzlichste Erfahrung in der PCB-Schaltungsdesign. .