Einführung in Leiterplattenlöten

Leiterplatte, Leiterplatte, Leiterplatte, PCB-Löttechnologie in den letzten Jahren, die Entwicklung des elektronischen Industrieverfahrens, können Sie feststellen, dass ein offensichtlicher Trend die Reflow-Löttechnologie ist. Grundsätzlich können herkömmliche Steckteile auch reflow-lötet werden, was allgemein als Durchgangslochreflow-Löten bezeichnet wird. Der Vorteil ist, dass alle Lötstellen gleichzeitig fertiggestellt werden können, was die Produktionskosten senkt. Temperaturempfindliche Bauteile begrenzen jedoch den Einsatz von Reflow-Löten, egal ob Interposer oder SMD. Dann wandten sich die Menschen der Wahl des Schweißens zu. In den meisten Anwendungen kann selektives Löten nach Reflow-Löten verwendet werden. Dies ist eine wirtschaftliche und effektive Möglichkeit, die verbleibenden Steckteile zu vervollständigen und ist vollständig kompatibel mit zukünftigen bleifreien Löten

1. Die Lötbarkeit des Leiterplattenlochs beeinflusst die Schweißqualität

Schlechte Lötbarkeit der Leiterplattenlöcher führt zu falschen Lötfehlern, die die Parameter der Komponenten in der Schaltung beeinflussen, was zu einer instabilen Leitung der mehrschichtigen Leiterplattenkomponenten und inneren Drähten führt, wodurch die gesamte Schaltung ausfällt. Die sogenannte Lötbarkeit ist die Eigenschaft, dass die Metalloberfläche durch geschmolzenes Lot benetzt wird, das heißt, auf der Metalloberfläche, an der sich das Lot befindet, wird ein relativ gleichmäßiger kontinuierlicher glatter Haftfilm gebildet. Die wichtigsten Faktoren, die die Lötbarkeit von Leiterplatten beeinflussen, sind:

(1) The composition of die solder and the nature of the solder. Löten ist ein wichtiger Teil des schweißenden chemischen Behandlungsprozesses. Es besteht aus chemischen Materialien, die Flussmittel enthalten. Häufig verwendete niedrig schmelzende eutektische Metalle sind Sn-Pb oder Sn-Pb-Ag. Der Verunreinigungsgehalt muss um einen bestimmten Anteil kontrolliert werden, um zu verhindern, dass die durch die Verunreinigungen erzeugten Oxide durch das Flussmittel gelöst werden. Die Funktion des Flusses besteht darin, dem Lot zu helfen, die Oberfläche des zu lötenden Stromkreises zu benetzen, indem Wärme übertragen und Rost entfernt wird. Weißes Kolophonium und Isopropanol-Lösungsmittel werden im Allgemeinen verwendet. (2) The welding temperature and the cleanliness of the metal plate surface will also affect the weldability. Wenn die Temperatur zu hoch ist, die Lötdiffusionsgeschwindigkeit erhöht sich. Zur Zeit, es wird hohe Aktivität haben, das schnell die Leiterplatte und die geschmolzene Oberfläche des Lots oxidiert, mit Lötfehlern. Verunreinigungen auf der Oberfläche der Leiterplatte beeinflussen auch die Lötbarkeit und verursachen Defekte. Zu diesen Defekten gehören Zinnperlen, Blechkugeln, offene Schaltungen, schlechter Glanz, etc.

2. Schweißfehler verursacht durch Verzug

Leiterplatten und Bauteile verzweigen sich während des Schweißprozesses, und Defekte wie virtuelles Schweißen und Kurzschluss durch Spannungsverformung. Verzug wird oft durch das Temperaturungleichgewicht des oberen und unteren Teils der Leiterplatte verursacht. Für große Leiterplatten, Auch durch den Abfall des Eigengewichts des Boards kann es zu Verzerrungen kommen. Das gewöhnliche PBGA Gerät ist ca. 0.5mm von der Leiterplatte entfernt. Wenn das Gerät auf der Platine größer ist, Die Lötstelle wird für eine lange Zeit unter Spannung stehen, da die Leiterplatte abkühlt und die Lötstelle unter Spannung steht. Wenn das Gerät um 0 angehoben wird.1mm, Es wird ausreichen, um Schweißen offenen Kreislauf zu verursachen.

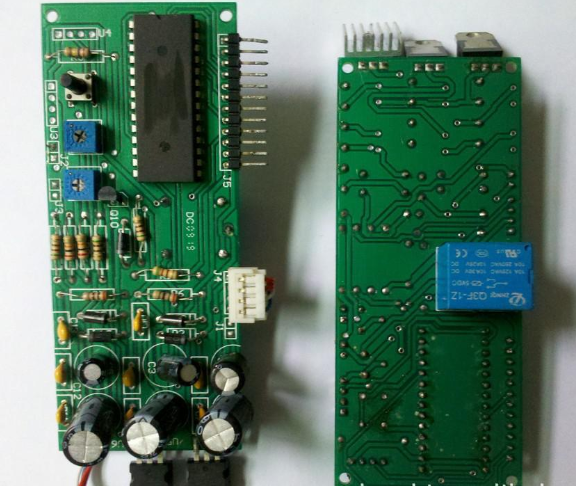

3. Das Design der Leiterplatte beeinflusst die Schweißenqualität

Im Layout, wenn die Leiterplattengröße zu groß ist, obwohl das Löten leichter zu kontrollieren ist, die gedruckten Linien sind lang, die Impedanz steigt, die Anti-Lärm-Fähigkeit wird reduziert, und die Kosten steigen; Gegenseitige Einmischung, wie elektromagnetische Störungen von Leiterplatten. Daher, the Leiterplattendesign must be optimized: (1) Shorten the wiring between high-frequency components and reduce EMI interference. (2) Components with heavy weight (such as more than 20g) should be fixed with brackets and then welded. (3) Heat dissipation issues should be considered for heating components to prevent defects and rework caused by large ÎT on the surface of the components, und die thermischen Komponenten sollten weit weg von der Heizquelle sein. (4) The arrangement of the components is as parallel as possible, das nicht nur schön, sondern auch leicht zu schweißen ist, und ist für die Massenproduktion geeignet. Die Platine ist als 4:3 Rechteck ausgeführt. Ändern Sie die Drahtbreite nicht, um Verkabelungsausfälle zu vermeiden. Wenn die Leiterplatte für eine lange Zeit erhitzt wird, Die Kupferfolie lässt sich leicht ausdehnen und abfallen. Daher, Vermeiden Sie die Verwendung großflächiger Kupferfolie.