System Level Packaging (SIP) ist keine einfache Verpackungstechnologie mehr, und diese Technologien umfassen PoP, CoC, WLP, TSV, Embedded Substrate usw. Es beinhaltet auch die Entwicklung anderer Verpackungsverfahren wie Drahtbonden, Flip-Chip, Micro Bumps usw.

Stapelpaket (PoP)

Stacked Encapsulation (PoP) kann mehr Funktionalität auf kleinerem Raum bieten. Stapelverpackungen können verwendet werden, um Multi-Chip-Pakete mit verschiedenen Funktionen zu entwickeln oder mehrere Speicherchips in einem Paket mit erhöhter Kapazität zu platzieren. Mit der System Level Encapsulation (SiP) lassen sich verschiedene Systemkomponenten in einem Paket realisieren. Diese Technologien ermöglichen es Halbleiterunternehmen, Produkte mit hoher Wertschöpfung zu schaffen und gleichzeitig den vielfältigen Anforderungen des Marktes gerecht zu werden.

Das Stapeln von Paketen ist der Prozess des vertikalen Stapelns von Paketen. Paket to Paket Stacking (PoP) ist die am häufigsten verwendete Stapelmethode und wurde in mobilen Geräten weit verbreitet. Für PoP in mobilen Geräten können die Arten und Funktionen von Chips, die in der oberen und unteren Verpackung verwendet werden, variieren, und Chiphersteller können auch unterschiedlich sein.

Die allgemeine PoP, die obere Verpackung umfasst hauptsächlich Speicherchips, die von Halbleiterlagerfirmen hergestellt werden, während die gestapelte Verpackung unten hauptsächlich Chips mit mobilen Prozessoren enthält. Da Verpackungen von verschiedenen Herstellern hergestellt werden, ist vor dem Stapeln eine Qualitätskontrolle erforderlich. Auch wenn nach dem Stapeln Defekte auftreten, können defekte Bauteile zur Nacharbeit durch neue Verpackungen ersetzt werden.

Chip on Chip(CoC)

COC (Chip on Chip) ist eine Technologie, die mehrere Chips in ein und demselben Paket kapselt. Durch das Stapeln mehrerer Chips zusammen kann es effektiv die Integration von Schaltungen verbessern, die Größe von Leiterplatten reduzieren und die Leistung und Zuverlässigkeit von Schaltungen verbessern.

Im COC-Verpackungsprozess besteht der erste Schritt darin, die Chips auszuwählen und zu testen. Chipauswahl bezieht sich auf die Auswahl von Chips, die die Anforderungen einer großen Charge von Chips erfüllen, die strenge Tests und Screening erfordert, um die Qualität und Leistung der Chips zu gewährleisten. Anschließend werden mehrere Chips mithilfe präziser Positionier- und Stapeltechniken zu einem Ganzen gestapelt. Während des Stapelprozesses werden präzise Positioniervorrichtungen und Klebstoffe benötigt, um die genaue Positionierung der Späne zu gewährleisten und die Stabilität während des Verpackungsprozesses zu gewährleisten.

Der Schlüssel zur COC-Verpackungstechnik liegt in der Verbindung von Chips. Nach dem Stapeln ist es notwendig, die Chips elektrisch anzuschließen, um Datenübertragung und Kommunikation zwischen ihnen zu erreichen. Dies wird in der Regel durch Mikrolöten oder Kabelverbindungen erreicht. Mikrolöten ist die Verwendung von winzigen Lötstellen, um die Pins zwischen Chips zu verbinden, während Kabelverbindung die Verwendung von kleinen Metalldrähten ist, um die Pins zwischen Chips zu verbinden. Diese Verbindungen erfordern eine präzise Bedienung und hohe technische Anforderungen, um ihre Zuverlässigkeit und Stabilität zu gewährleisten.

Nachdem die Verpackung abgeschlossen ist, ist es notwendig, Aussehen Behandlung und Prüfung durchzuführen. Aussehen Behandlung bezieht sich auf die Verschönerung und den Schutz des Verpackungskörpers, um das Aussehen und die Qualität des Produkts zu verbessern. Dieser Prozess umfasst das Beschichten, Polieren und Polieren des Verpackungskörpers sowie das Etikettieren und Verpacken. Die Prüfung bezieht sich auf die Durchführung von elektrischen Leistungs- und Zuverlässigkeitstests an verpackten Chips, um sicherzustellen, dass sie Designanforderungen erfüllen und ordnungsgemäß funktionieren können.

Die Anwendung der COC-Verpackungstechnologie ist sehr umfangreich. Es kann zum Verpacken verschiedener integrierter Schaltungen verwendet werden, einschließlich Mikroprozessoren, Speicher, Kommunikationschips usw. Der COC-Verpackungsprozess kann die Integration und Leistung von Schaltungen verbessern, die Größe von Leiterplatten reduzieren, den Systemstromverbrauch senken und die Systemzuverlässigkeit und -stabilität verbessern. Daher ist es in der Herstellung von elektronischen Produkten wie Mobiltelefonen, Tablets, Fernsehern und Kameras weit verbreitet.

COC-Verpackungsprozess ist eine Technologie, die mehrere Chips in ein und demselben Paket kapselt. Es erreicht Schaltungsintegration, Miniaturisierung und hohe Leistung durch Prozesse wie Chipauswahl, Stapeln und Anschluss sowie Aussehen Verarbeitung und Prüfung. Der COC-Verpackungsprozess spielt eine wichtige Rolle bei der Herstellung elektronischer Produkte, da er nicht nur die Leistung und Zuverlässigkeit von Schaltungen verbessert, sondern auch die Größe und den Stromverbrauch von Produkten reduziert.

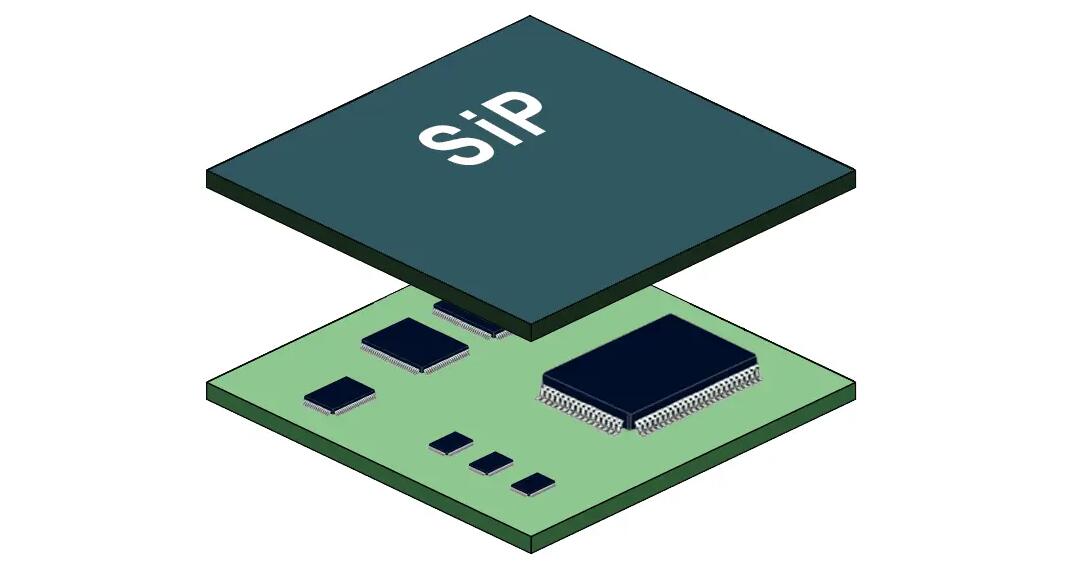

Verpackung auf Systemebene (SIP)

Die Vorteile von System Level Packaging (SIP)

1. Hohe Verpackungseffizienz, SiP-Verpackungstechnologie fügt mehrere Chips innerhalb des gleichen Pakets hinzu, reduziert das Verpackungsvolumen erheblich und verbessert die Verpackungseffizienz.

2.Das Produkt hat einen kurzen Startzyklus, und da SIP-Verpackungen sich von SOC unterscheiden, erfordert es kein Layout und Routing auf Layoutebene, wodurch die Komplexität von Design, Verifizierung und Debugging reduziert und die Systemimplementierungszeit verkürzt wird. Selbst wenn teilweise Konstruktionsänderungen erforderlich sind, ist es viel einfacher und einfacher als Soc.

3. Gute Kompatibilität, SIP-Verpackung kombiniert Chips aus verschiedenen Prozessen und Materialien zu einem System, das eine Traumkombination von eingebetteten integrierten passiven Komponenten erreichen kann. Passive Komponenten, die derzeit in drahtlosen und tragbaren elektronischen Geräten verwendet werden, können mit mindestens 30-50% Î eingebettet werden."

4. Durch die Verringerung der Systemkosten kann SIP stromarme und rauscharme Systemverbindungen bereitstellen, und das Arbeiten mit höheren Frequenzen kann eine breitere Bandbreite und fast die gleiche Busbandbreite wie SOC erreichen. Ein dediziertes integriertes Schaltungssystem, das SIP-Verkapselungstechnologie verwendet, kann mehr Systementwurfs- und Produktionskosten sparen als SOC.

5. Die physische Größe ist klein, und die Dicke der SIP-Verpackung nimmt ständig ab. Die fortschrittlichste Technologie kann ultradünnes Verpacken mit nur 1.0mm Stärke für Fünfschichtstapelchips erreichen und das Gewicht der dreischichtigen Chipverpackung um 35%.

6. Hohe elektrische Leistung, SIP-Verpackungstechnologie kann mehrere Pakete in einem kombinieren, wodurch die Gesamtzahl der Lötstellen erheblich reduziert wird, Verpackungsvolumen und -gewicht erheblich reduziert, Komponentenverbindungswege verkürzt und somit die elektrische Leistung verbessert wird.

7. Weit verbreitet, SIP-Verpackung unterscheidet sich von der traditionellen Chipverpackung. Es kann nicht nur digitale Systeme verarbeiten, sondern auch in Bereichen wie optische Kommunikation, Sensoren und mikroelektromechanische Systeme (MEMS) eingesetzt werden.

Die Hauptanwendungsgebiete der SIP-Verkapselung

SIP hat eine breite Palette von Anwendungen, einschließlich drahtloser Kommunikation, Automobilelektronik, medizinische Elektronik, Computer, Militärelektronik, etc. Der am weitesten verbreitete Bereich unter ihnen ist die drahtlose Kommunikation.

SIP wurde zuerst und am weitesten verbreitet im Bereich der drahtlosen Kommunikation eingesetzt. Im Bereich der drahtlosen Kommunikation werden die Anforderungen an funktionale Übertragungseffizienz, Lärm, Volumen, Gewicht und Kosten immer höher, was die drahtlose Kommunikation zwingt, sich in Richtung kostengünstiger, tragbarer, multifunktionaler und leistungsstarker Richtungen zu entwickeln.

SIP ist eine ideale Lösung, die die Vorteile bestehender Kernressourcen und Halbleiterproduktionsprozesse kombiniert, Kosten senkt, die Markteinführungszeit verkürzt und Schwierigkeiten wie Prozesskompatibilität, Signalmischung, Störgeräusche, elektromagnetische Störungen usw. in SOC überwindet.

SIP-Verkapselungstechnologie ist eine fortschrittliche Systemintegrations- und Verkapselungstechnologie. Verglichen mit anderen Verkapselungstechnologien hat SIP-Technologie eine Reihe einzigartiger technischer Vorteile, die den Entwicklungsanforderungen von leichteren, kleineren und dünneren elektronischen Produkten heute gerecht werden. Es hat einen breiten Anwendungsmarkt und Entwicklungsperspektiven im Bereich der Mikroelektronik.