(1)電子系統設計面臨的挑戰

隨著系統設計複雜度和集成度的大規模新增,電子系統設計者都在從事100MHZ以上的電路設計,匯流排的工作頻率已經達到或超過50MHZ,有的甚至超過100MHZ。 現時,約50%的設計具有50MHz以上的時鐘頻率,近20%的設計具有120MHz以上的時鐘頻率。

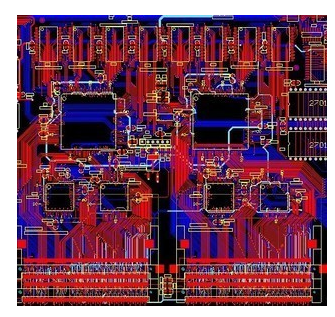

當系統在50MHz下工作時, 會出現傳輸線效應和信號完整性問題; 當系統時鐘達到120MHz時, 除非使用高速電路設計知識, 基於傳統方法設計的PCB將無法工作. 因此, 高速PCB 設計科技已成為電子系統設計者必須採用的設計方法. 設計過程的可控性只能通過使用高速電路設計者的設計科技來實現.

(2)什麼是高速電路

一般認為,如果數位邏輯電路的頻率達到或超過45MHZ~50MHZ,並且在該頻率以上工作的電路已占整個電子系統的一定份額(例如,1/3),則稱為高速電路。

事實上,訊號邊緣的諧波頻率高於訊號本身的頻率。 正是訊號的上升沿和下降沿(或訊號跳躍)導致了訊號傳輸中的意外結果。 囙此,一般認為,如果線路傳播延遲大於數位信號驅動端上升時間的1/2,則此類訊號被視為高速訊號,並產生傳輸線效應。

訊號傳輸發生在訊號狀態變化的瞬間,例如上升或下降時間。 訊號從驅動端到接收端經過一段固定的時間。 如果傳輸時間小於上升或下降時間的1/2,則來自接收端的反射訊號將在訊號改變狀態之前到達驅動端。 相反,在訊號改變狀態後,反射訊號將到達驅動端。 如果反射訊號很强,疊加波形可能會改變邏輯狀態。

(3)高速訊號的確定

在上面,我們定義了傳輸線效應發生的先決條件, 但是我們如何知道線路延遲是否大於1/2驅動端的訊號上升時間? 通常地, 訊號上升時間的典型值可在設備手册中給出, 訊號傳播時間由電路中的實際佈線長度决定 PCB設計. Correspondence between signal rise time and allowable wiring length (delay).

PCB上每組織英寸的延遲為0.167ns。 然而,如果網絡電纜上設定了許多過孔、許多設備管脚和許多約束,則延遲將新增。 通常,高速邏輯器件的訊號上升時間約為0.2ns。 如果板上有砷化鎵晶片,則最大佈線長度為7.62mm。

設Tr為訊號上升時間,Tpd為訊號線傳播延遲. 如果Tr– 4Tpd, 訊號落在安全區域. 如果2Tpd–Tr–4Tpd, 訊號落在不確定區域. 如果Tr–2Tpd, 訊號落在問題區域. 對於落在不確定區域和問題區域的訊號, high-speed PCB佈線 methods should be used.