EMC注意事項 PCB設計

隨著電子時代的發展, 人類生活環境中的電磁波源越來越多, 比如無線電廣播, 電視機, 微波通信; 家用電器; 輸電線路的工頻電磁場; 高頻電磁場, 等. 當這些電磁場的場強超過一定限制且作用時間足够長時, 可能危害人體健康; 同時, 它還會干擾其他電子設備和通信. 在這方面, 需要保護. 在開發過程中,經常會提出電磁干擾和遮罩等概念, 電子產品的生產和使用. 電子產品在正常運行期間的覈心是電路板與安裝在其上的零部件之間的協調工作過程. 提高電子產品的性能指標,减少電磁干擾的影響,具有十分重要的意義.

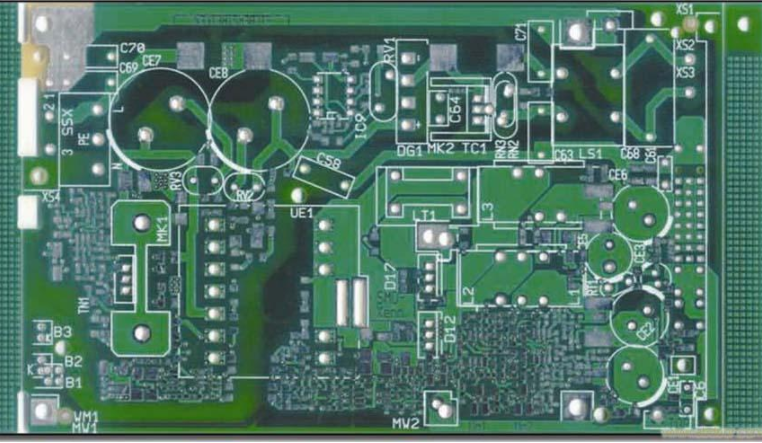

1. PCB板設計

印刷電路板(PCB)是電子產品中電路元件和器件的支撐。 它提供電路組件和設備之間的電力連接。 它是各種電子設備的最基本組件。 印刷電路板的效能直接關係到電子學。 設備的質量和效能是好是壞。 隨著集成電路、表面貼裝科技和微組裝科技的發展,越來越多的高密度、多功能電子產品出現,導致PCB上佈線複雜,零部件多,安裝密集,不可避免地會造成它們之間的干擾。 由於電磁干擾越來越嚴重,囙此抑制電磁干擾的問題已成為電子系統能否正常工作的關鍵。 同樣,隨著電子技術的發展,PCB的密度越來越高,PCB設計的質量對電路的干擾和抗干擾能力有很大的影響。 為了獲得最佳的電子電路效能,除了元器件的選擇和電路設計外,良好的PCB設計也是電磁相容性的一個非常重要的因素。

1.1合理的PCB層設計

根據電路的複雜性,合理選擇PCB的層數可以有效地减少電磁干擾,大大减小PCB的尺寸以及電流回路和分支佈線的長度,並大大减少訊號之間的交叉干擾。 實驗表明,當使用相同的資料時,四層板的雜訊比雙層板低20dB。 然而,層數越高,製造過程越複雜,製造成本越高。 在多層板佈線中,最好在相鄰層之間使用“良好”形狀的網狀佈線結構,即相鄰層的各個佈線方向相互垂直。 例如,印製板的上側水准佈線,下側垂直佈線,然後通過過孔連接。

1.2合理的PCB尺寸設計

當 PCB板 尺寸太大, 印刷線路將新增, 阻抗將新增, 抗雜訊能力會降低, 設備體積會新增,成本也會相應新增. 如果尺寸太小, 散熱不好, 相鄰線路易受干擾. 一般來說, the mechanical layer (Mechanical Layer) determines the physical frame, 那就是, PCB的外形尺寸, and the Keepout Layer (Keepout Layer) is forbidden to determine the effective area of layout and wiring. 通常地, 根據電路功能單元的數量, 電路的所有部件都是集成的, 最好的形狀和尺寸 PCB板 最終確定. 通常選擇矩形, 縱橫比為3:2. 當電路板的尺寸大於150 mmx200 mm時, 應考慮電路板的機械強度.

2 PCB佈局

在PCB設計中,產品設計者往往只注重新增密度、减少佔用空間、製作簡單,或追求美觀和均勻佈局,忽視電路佈局對電磁相容性的影響,導致大量訊號輻射到空間中形成相互干擾。 不良的PCB佈局可能會導致更多的電磁相容性問題,而不是消除這些問題。

電子設備中數位電路、類比電路和功率電路的元件佈局和佈線的特點不同,它們產生的干擾和抑制干擾的方法也不同。 由於高頻和低頻電路的頻率不同,它們的干擾和抑制干擾的方法也不同。 囙此,在元件佈局中,數位電路、類比電路和功率電路應分開放置,高頻電路和低頻電路應分開。 如果可能,應將其隔離或單獨製成電路板。 在佈局中,應特別注意强弱訊號的設備分佈和訊號傳輸方向。

2.1 PCB組件佈局

PCB元件的佈局與其他邏輯電路相同,相互關聯的元件應盡可能靠近,以獲得更好的抗雜訊效果。 元件在印刷電路板上的位置應充分考慮抗電磁干擾問題。 原則之一是組件之間的導線應盡可能短。 在佈局中,類比信號部分、高速數位電路部分和雜訊源部分(如繼電器、大電流開關等)應合理分離,以最小化彼此之間的訊號耦合。

時鐘發生器、晶體振盪器和CPU時鐘輸入端子都容易產生雜訊,囙此它們應該彼此靠近。 易產生雜訊的設備、低電流電路和高電流電路應盡可能遠離邏輯電路。 如果可能,應製作另一塊電路板,這一點非常重要。

PCB元件的總體佈局要求:電路元件和訊號路徑的佈局必須最大限度地减少不必要訊號的耦合。

1)低電平訊號通道不能接近高電平訊號通道和未濾波的電力線,包括可能產生瞬態過程的電路。

2)分離低電平類比電路和數位電路,以避免類比電路、數位電路和電源公共回路之間的公共阻抗耦合。

3)高速、中速和低速邏輯電路使用PCB上的不同區域。

4)在佈置電路時,訊號線長度應儘量短。

5)確保相鄰板之間、同一板的相鄰層之間以及同一層上的相鄰接線之間沒有過長的平行訊號線。

6)電磁干擾(EMI)濾波器應盡可能靠近電磁干擾源,並放置在同一電路板上。

7)直流/直流變換器、開關元件和整流器應盡可能靠近變壓器,以儘量減少其導線長度。

8)將調壓元件和濾波電容器盡可能靠近整流二極體。

9)印製板根據頻率和電流開關特性進行劃分,雜訊元件和非雜訊元件之間的距離應更遠。

10)對雜訊敏感的接線不應與大電流、高速開關線平行。

11)部件佈局應特別注意散熱問題。 對於大功率電路,應盡可能遠地放置功率管和變壓器等加熱部件,以便於散熱。 不要集中在一個地方,並且不要將高電容太靠近,以避免電解液過早老化。

2.2 PCB佈線

PCB的組成是垂直堆疊上的層壓、佈線和預浸料的一系列多層結構。 在多層PCB中,為了便於調試,訊號線將佈置在最外層。

在高頻情况下,印刷電路板上連接器的佈線、過孔、電阻器、電容器以及分佈電感和分佈電容不容忽視。 電阻會引起高頻訊號的反射和吸收。 軌跡的分佈電容也將發揮作用。 當軌跡的長度大於雜訊頻率的相應波長的1/20時,會發生天線效應,並通過軌跡發射雜訊。

印刷電路板的大多數接線都是通過過孔完成的。 一個通孔可以產生約0.5 pF的分佈電容,减少通孔的數量可以顯著提高速度。

集成電路的封裝資料本身引入了2到6pF的電容。 電路板上的連接器具有520 nH的分佈電感。 雙直列24針集成電路插座引入4-18 nH分佈電感。

為避免PCB佈線分佈參數的影響,應遵循的一般要求:

1)新增記錄道間距以减少電容耦合的串擾。

2)在雙面板佈線中,兩側的導線應垂直、傾斜或彎曲,以避免相互平行,以减少寄生耦合; 應盡可能避免使用印刷導線作為電路的輸入和輸出。 為了避免迴響,最好在這些導線之間添加接地線。

3)將敏感高頻線遠離高雜訊電力線,以减少相互耦合; 高頻數位電路跡線應更薄、更短。

4)加寬電源線和地線,以降低電源線和地線的阻抗。

5)嘗試使用45°折疊線而不是90°折疊線,以减少高頻訊號的外部發射和耦合。

6)地址線或數據線的長度不應相差太大,否則必須人為彎曲短線部分以進行補償。

7)注意大電流訊號之間的隔離, 高壓訊號和小訊號 (隔離距離與要承受的耐受電壓有關。通常情况下,在2 kV時,配電盤之間的距離為2 mm,比率在此基礎上計算。例如,為了承受3 kV耐受電壓試驗,高低壓線之間的距離應大於3.5 mm。在許多情况下,為了避免爬電,印刷電路上的高低壓線 應打開電路板。 槽)。

3 PCB中的電路設計

在設計電子電路時,更多地考慮產品的實際效能,而不是過多地考慮產品的電磁相容特性、電磁干擾抑制和電磁抗干擾特性。 為了在使用電路原理圖進行PCB佈局時達到電磁相容的目的,必須採取必要的措施,即在電路原理圖的基礎上新增必要的附加電路,以提高其產品的電磁相容效能。 以下電路措施可用於實際PCB設計:

1)可以在PCB軌跡上串聯電阻器,以降低控制訊號線下邊緣的過渡速率。

2)嘗試為繼電器等提供某種形式的阻尼(高頻電容器、反向二極體等)。

3)過濾進入印製板的訊號,並將訊號從高雜訊區域過濾到低雜訊區域。 同時,使用一系列終端電阻來减少訊號反射。

4)MCU的無用端應通過相應的匹配電阻連接到電源或接地,或定義為輸出端。 集成電路中應連接到電源和接地的端子必須連接,並且不得浮動。

5)不要留下未使用的柵極電路的輸入端子,而是通過相應的匹配電阻器連接到電源或接地。 未使用的運算放大器的正極輸入端子接地,負極輸入端子連接到輸出端子。

6)為每個集成電路設定高頻去耦電容器。 必須在每個電解電容器上添加一個小型高頻旁路電容器。

7)使用大容量鉭電容器或聚酯電容器代替電解電容器作為電路板上的充放電儲能電容器。 當使用管狀電容器時,外殼應接地。

4結論

隨著科學技術的日益發展, 各種電子設備的小型化和智能化已成為主流趨勢. 同時, 電子產品或設備的操作環境將變得越來越複雜. 抗干擾科技和電磁相容科技也需要不斷發展和成熟. PCB設計ers和 電路板製造商必須充分重視實際應用.