Cadence PCB設計是一款大型EDA軟件,幾乎可以完成電子設計的所有方面,包括ASIC設計、FPGA設計和PCB板設計。

Cadence PCB設計方法

如今,越來越多的高速設計正在採用一種更有利於加快開發週期的更有效的方法。 首先,建立一套符合設計性能指標的物理設計規則,並使用這些規則來限制PCB佈局和佈線。在安裝設備之前,首先進行類比設計。

在這個虛擬測試中,設計者可以比較設計名額來評估效能。 這些關鍵的先決條件是建立一套性能指標的物理設計規則,而規則的基礎是基於模型的模擬分析和對電力特性的準確預測,囙此不同階段的模擬分析非常重要。

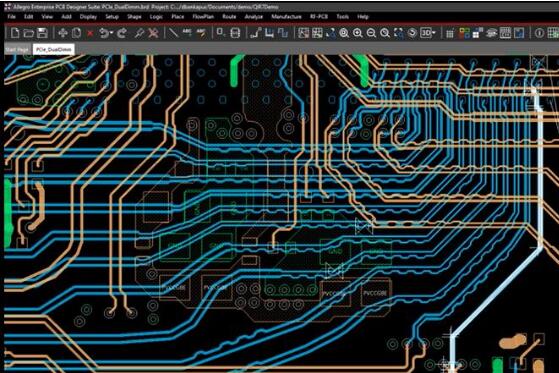

Cadence在PCB設計工作室發佈了一個非常實用的工具選項,用於高速電路設計和信號完整性分析-Allegro PCB。 該模擬軟件可用於根據層的分類、PCB的介電常數、介質的厚度、訊號層的位置和線寬來確定電路板線路是否屬於微帶線、帶狀線、寬帶耦合帶狀線等。並根據不同的計算公式,自動計算訊號線的阻抗和訊號線的反射、串擾、電磁干擾等,從而約束佈線,確保PCB基板的信號完整性。

佈線時,使用Interconnect Designer工具設定各種約束條件,其中包括廣泛的物理和電力性能參數,如常見的PCB線寬、過孔數量、阻抗範圍、峰值串擾、過沖特性、訊號延遲、阻抗匹配等。使用模擬結果來確定時序、信號完整性和電磁相容性。根據時間特性和其他相關問題進行優化設計。

Cadence軟體發展了用於高速PCB設計的設計流程。 其主要思想是使用良好的類比分析設計來防止問題的發生,並嘗試在PCB生產之前解决所有可能的問題。

與傳統的設計過程相比,主要區別在於過程中新增了控制節點,可以有效地控制設計過程。 它集成了原理圖設計、PCB佈局和佈線以及高速模擬分析,可以解决設計各個階段的電力效能相關問題。 通過分析時序、信噪比、串擾、功率結構和電磁相容性等各種因素,可以在佈局和佈線之前對系統的信號完整性、功率完整性、電磁干擾等問題進行優化設計。

Cadence PCB設計的優勢

1)可靠、可擴展且經濟高效的PCB編輯和佈線解決方案,可根據設計要求不斷更新。

2)提供一個完整的互連環境,從基本/高級佈局和佈線到戰略規劃和全球佈線。

3)使用高速規則/約束加速高級設計。

4)包含一套全面的功能組合。

5)包含從前端到後端的約束管理系統,用於創建、管理和確認約束。

6)通過集成應用軟體提高設計效率。

7)可以實現從前端到後端的緊密集成。

Cadence PCB設計軟體,操作簡單,實用性強。 它可以完成原理圖設計、原理圖符號製作、PCB元件封裝設計、板框設定、元件佈局、PCB板佈線和輸出檔案。