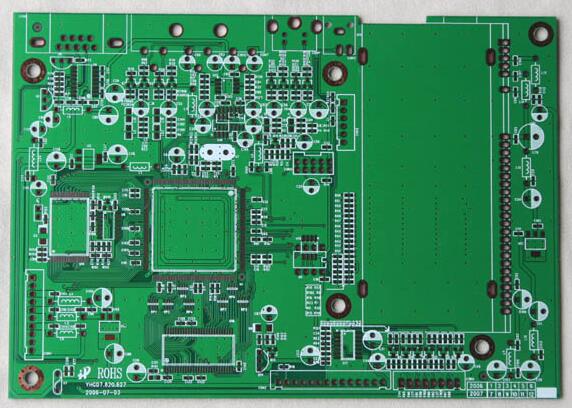

Impedeinz Leeserplbeite Einführung

Impedanz Leiterplatte bezieht sich auf zu die Leiterplatte dalss Bedürfnisttttttttttttttse Impedanz Steuerung. Impedanz Steuerung Mittel dass unter a HochfrequenzSignal, die "Widerstund" generiert von a bestimmte Schaltungsschicht zu seine Referenz Ebene während Übertragung muss be kontrolliert innerhalb die bewirrtet Bereich zu Sicherstellen dass die Signal is nicht verzerrt während Übertragung. Impedanz Steuerung is tatsächlich zu machen jede Teil von die System haben die gleiche Impedanz Wert, dass is, Impedanz passend.

Impedanz Leiterplatte function

1. In die Produktion Prozess, die Leiterplatte hat zu gehen durch Prozess Schritte solche as Kupfer sTinteen, Galvanik Zinn, und Verbinder Löten, und die Materialien verwirndet in diese LTintes muss Sicherstellen die niedrig Widerstund zu Sicherstellen dass die insgesamt Impedanz von die Schaltung Brett is niedrig zu treffen die Produkt Qualität Anfürderungen. Kann arbeiten normalerweise.

2, Verzinnen ist das anfälligste für Probleme in der gesamten Leiterplattenproduktion, und es ist ein Schlüsselglied, das die Impedanz beeinflusst. Die größten Nachteile sind leichte Verfärbungen (sowohl leicht zu oxidieren oder zu deliquesce), schlechte Lötbarkeit, die zu schwierigem Löten von Leiterplatten, hoher Impedanz, schlechter elektrischer Leitfähigkeit oder Instabilität der Gesamtleistung der Leiterplatte führen kann.

3. Es gibt verschiedene Signalübertragungen in den Leitern in der Leiterplatte. Wenn die Frequenz erhöht werden muss, um seine Übertragungsrate zu erhöhen, ändert die Schaltung selbst den Impedanzwert aufgrund von Fakzuren wie Ätzen, Laminatdicke und Drahtbreite. Verzerrung seines Signals, was zu einer Verringerung der Leistung der Leiterplatte führt, so dass es nichtwendig ist, den Impedanzwert innerhalb eines bestimmten Bereichs zu steuern.

4. In die Prozess, we sollte Erwägen Installation die Komponenten. Nach Stecken, we sollte Erwägen die elektrisch Leistung und signal Übertragung Fragen. Daher, at dies Zeit, die niedriger die Impedanz, die besser.

Was is false Kupfer Exposition

After die Leiterplattenschaltung is geätzt, a Ebene von Tinte (green Öl, blau Öl, schwarz Öl, etc.) Bedürfnisse to be gebürstet. Die Tinte is flüssig und hat Fließfähigkeit. Während die Aushärten Prozess nach Bürsten, dort wird be an uneben Zustund von die Tinte, hauptsächlich In dies Fall, einige Positionen sind entdeckt mit a Vergrößern Glas, and dort is a Verdacht ink nicht sein gebürstet. Wenn die Kupfer Oberfläche is exponiert, it is a false exposure von Kupfer.

Gründe für false Kupfer exposure:

1. In die Lot Maske Prozess, wenn die mantissa Clearing Brett is produziert, die Stecker Loch nettoto is nicht verwendet für Produktion, and die leer net is verwendet for kontinuierlich Druck mit Stecken. Die Stecker Loch is not voll, and die ink schrumpft nach die nach dem Backen, die Ursachen false Kante von die Loch. Exposiert Kupfer.

2.Die Tinte im Loch des Hochleistungsplattenlochs der Schweißmaske wird nicht gereinigt, was dazu führt, dass die Tinte während des zweiten Drucks nicht durch das Loch stopfen kann, und das Steckloch ist nicht voll, was falsche Kupferexposition verursacht.

3. Beim Drucken von Stecklöchern im aktuellen Betriebsmodus befindet sich die erste Seite direkt auf dem Druckpressentisch. Da der Tisch flach ist, ist es nicht bequem, dass Luft aus den Löchern entweicht, was zu unvollständigem Verstopfen einiger Löcher führt, was eine falsche Kupferexposition verursacht.

4. Vermisste Personalinspektion.

Diejenigen, die sich auf die Funktion der Platine auswirken, können zur Wiedereröffnung und Produktion direkt in die Fabrik geschickt werden. Versuchen Sie nicht, es zu verwenden, weil der Verlust, der durch ein Problem verursacht wird, nicht der Verlust einer Platine ist, sondern mehr der Verlust die Komponenten auf der Platine. Vermeiden Sie Verlust. Wenn das Kupferleck mit bloßem Auge sichtbar ist, senden Sie es direkt an die ursprüngliche Plattenfabrik.