Im modernen elektronischen Design ist PCB-Design entscheidend, und der Bus als Schlüsselkanal für die Kommunikation zwischen verschiedenen Geräten bietet die Grundlage für die Leistung und Effizienz des PCB-Designs. In diesem Artikel werden wir die Eigenschaften, Vor- und Nachteile sowie Anwendungsszenarien von parallelen und seriellen Bussen im Hochgeschwindigkeits-PCB-Design eingehend diskutieren, um Konstrukteuren zu helfen, den richtigen Bustyp besser zu verstehen und auszuwählen.

Ein Bus ist ein gemeinsamer physikalischer Pfad für die Kommunikation zwischen zwei oder mehr Geräten, eine Sammlung von Signalleitungen und eine gemeinsame Verbindung zwischen mehreren Komponenten für die Übertragung von Informationen zwischen ihnen. Es gibt zwei Haupttypen von Bussen basierend auf ihrer Betriebsart: Parallelbusse und serielle Busse.

Parallelbusse sind so konzipiert, dass mehrere Bits von Daten gleichzeitig übertragen werden können. Diese Busstruktur ähnelt einer geräumigen Fahrbahn, die mehrere Fahrzeuge gleichzeitig aufnehmen kann, und wird typischerweise in Situationen verwendet, in denen die Datenübertragung anspruchsvoller ist. Der Vorteil eines Parallelbusses ist, dass die Datenübertragung schnell erfolgt, da mehrere Signale gleichzeitig übertragen werden können. Bei steigenden Datenübertragungsraten treten jedoch Probleme mit der Signalintegrität und Interferenzen auf. Parallele Busverbindungen erfordern mehr Signalleitungen, was zu einer erhöhten Komplexität des Designs führt. Übersprechen und Verzögerungen zwischen Signalen können bei Hochfrequenzbetrieben nicht ignoriert werden.

Im Gegensatz zu parallelen Bussen übertragen serielle Busse Daten nacheinander in Bitreihenfolge. Serielle Signalisierung verwendet normalerweise weniger Signalleitungen, was die Verkabelung einfacher und klarer macht. Da nur ein oder mehrere Leitungen für die Datenübertragung benötigt werden, sind serielle Busse besonders wichtig, um den Platzbedarf auf der Leiterplatte zu reduzieren und die Komplexität des fertigen Produkts zu reduzieren.

Serielle Busse sind im Allgemeinen resistenter gegen Störungen, insbesondere wenn Differentialsignale verwendet werden, bei denen jedes Paar Differentialdrähte aus einem positiven und einem negativen besteht, was die Signalintegrität verbessert. Obwohl serielle Busse weniger Bits pro Zeiteinheit übertragen, können höhere Datenraten durch höhere Ausbreitungsraten erreicht werden.

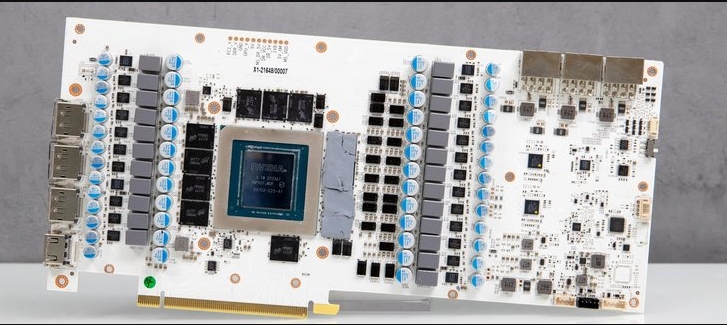

Parallelbusse eignen sich für Anwendungen, die eine hohe Bandbreite und geringe Latenz erfordern. Häufige Anwendungen sind die Übertragung von Daten innerhalb eines Computers und der Anschluss von leistungsstarken Peripheriegeräten wie Grafikkarten. Parallelbusse sind in der Lage, mehrere Bits von Daten gleichzeitig zu übertragen, was ihnen einen erheblichen Vorteil beim Umgang mit großen Datenmengen verschafft. Beispielsweise verwenden herkömmliche Computerbusse wie PCI und PCIe Parallelität für eine schnelle Datenübertragung. Bei hohen Betriebsfrequenzen können jedoch erhebliche Interferenzen zwischen parallelen Signalleitungen auftreten, so dass Konstrukteure bei der Verwendung paralleler Busse die Aufrechterhaltung der Signalintegrität und das Interferenzmanagement berücksichtigen müssen. Richtige Verkabelungs- und Signalkonditionierungstechniken können wirksam sein, um die Auswirkungen dieser Probleme zu minimieren.

Im Vergleich zu parallelen Bussen sind serielle Busse besser für die Ferndatenübertragung und den großen Datenaustausch geeignet. Mit einfacher Verkabelung und niedrigen Kosten sind serielle Busse eine der Hauptoptionen für moderne Kommunikation. Zu den Anwendungen gehören verschiedene Schnittstellenstandards wie I2C, SPI und USB, die häufig für die Konnektivität zwischen Sensoren, Mikrocontrollern und anderen Peripheriegeräten verwendet werden. Das Design des seriellen Busses bietet ihm einen Vorteil in Bezug auf Störfestigkeit, wodurch er für den Einsatz in Umgebungen mit starken elektromagnetischen Störungen geeignet ist. Beispielsweise ist CAN-Bus ein gängiges serielles Kommunikationsprotokoll, das in Automobil- und Industrieanwendungen verwendet wird, und seine robusten Fehlererkennungs- und Redundanzmechanismen sorgen für eine zuverlässige Datenübertragung in komplexen Umgebungen.

Es kann nur ein Stück Daten gleichzeitig übertragen werden, das ist wie eine schmale Straße, auf der nur ein Auto laufen kann. Die Daten müssen nacheinander übertragen werden, was wie eine lange Datenkette aussieht, also "seriell" genannt wird.

Das beste Beispiel für parallele Übertragung ist der Speicherchip DDR. Es verfügt über eine Reihe von Datenleitungen D0-D7 sowie DQS und DQM. Dieser Satz von Linien wird zusammen übertragen. Egal, welches Bit einen Fehler aufweist, die Daten werden nicht korrekt übertragen. Nur weitersenden. Daher muss jedes Kabel des Datenkabels gleich lang sein und es muss mehrmals gewickelt werden.

Die Seriendaten sind anders. Daten werden einzeln übertragen, und es gibt keine Verbindung zwischen Bits. Es gibt keinen Fehler in diesem Bit und das nächste Bit kann nicht übertragen werden. Parallele Daten sind eine Reihe von Daten, bei denen ein Bit falsch ist und der gesamte Datensatz nicht funktioniert.

Anforderungen an die Leiterplattenverdrahtung

Anforderungen an parallele Busverdrahtung:

(1) Es wird empfohlen, dass der Bus vorzugsweise intern verdrahtet ist, und der Abstand zwischen dem Bus und anderen Verkabelungen sollte so weit wie möglich erhöht werden.

(2) Zusätzlich zu speziellen Anforderungen wird die einzeilige Entwurfsimedanz garantiert 50 Ohms zu sein, und die Differenzentwurfsimedanz wird garantiert 100 Ohms zu sein.

(3) Es wird empfohlen, dass dieselbe Gruppe von Bussen die gleiche Verdrahtungslänge beibehält und einer bestimmten Zeitbeziehung zur Taktleitung folgt und die Verdrahtungslänge unter Bezugnahme auf die starken Ergebnisse der Zeitanalyse steuert.

(4) Es wird empfohlen, so nah wie möglich an der I/O-Stromversorgungs- oder GND-Bezugsebene dieser Gruppe von Bussen zu sein, um die Integrität der Bezugsebene zu gewährleisten.

(5) Ein Bus mit einer Anstiegszeit von weniger als 1ns benötigt eine vollständige Bezugsebene und darf die Partition nicht überqueren.

(6) Es wird empfohlen, dass sich der untere Adressbus auf die Anforderungen an die Taktverdrahtung bezieht.

(7) Der Abstand des Schlangenwickeldrahts darf nicht kleiner als das Dreifache der Linienbreite sein.

Anforderungen an die serielle Busverdrahtung von Leiterplatten mit hoher Geschwindigkeit

Für einen seriellen Bus mit einer Frequenz über 100Mbps müssen neben der Einhaltung der allgemeinen Übersprecherregeln und Verdrahtungsregeln für Parallelbusse einige zusätzliche Anforderungen bei der Verdrahtung berücksichtigt werden:

(1) Der serielle Hochgeschwindigkeits-PCB-Bus muss den Verdrahtungsverlust berücksichtigen und die Leitungsbreite und Leitungslänge bestimmen.

(2) Es wird empfohlen, dass die Leitungsbreite unter normalen Umständen nicht kleiner als 5mil ist, und die Verkabelung sollte so kurz wie möglich sein.

(3) Mit Ausnahme der Fanout-Durchgänge sollte der serielle Hochgeschwindigkeitsbus nicht gestanzt und gewechselt werden.

(4) Wenn die Geschwindigkeit der am seriellen Bus beteiligten Stecknadeln über 3.125Gbps liegt, sollte das Antipad optimiert werden, um den Einfluss der Nichtstrahlung zu verringern, die durch diskontinuierliche Impedanz verursacht wird.

(5) Es wird empfohlen, beim Wechsel der Schichten der Hochgeschwindigkeits-seriellen Busverdrahtung die Verdrahtungsschicht mit dem kleinsten Durchgangsstub zu wählen. Für das Signal an den Stecker wird bei begrenztem Verdrahtungsraum bevorzugt die Verdrahtungsschicht mit dem kurzen Durchgangsstub dem sendenden Ende zugeordnet.

(6) Es wird empfohlen, dass, wenn die Rate 3.125Gbps oder höher ist, ein Erdloch neben dem Signal durch gebohrt wird, und der AC-Kupplungskondensator sollte auch speziell für das Anti-Pad behandelt werden.

(7) Wenn die Hochgeschwindigkeitssignaldurchgänge durch Rückbohren verarbeitet werden, ist es notwendig, den Einfluss der Verringerung der Stromdurchflusskapazität der Leistungsgrundebene und der Erhöhung der Filterschleifeninduktivität zu berücksichtigen, nachdem der Strömungsengpass verengt ist.

(8) Das Hochgeschwindigkeitssignal vermeidet die Trennlinie der ebenen Schicht, und der horizontale Abstand zwischen dem Rand der Signallinie und dem Rand der Trennlinie ist garantiert, 3W zu sein.

(9) Hochgeschwindigkeitssignale in beide Richtungen sollten nicht gekreuzt und geleitet werden.