Das Leiterplattendesign ist eine sehr zeit- und zeitaufwändige Aufgabe. Jedes Problem erfordert, dass Ingenieure das gesamte Design auf Komponentenbasis überprüfen. Es kann gesagt werden, dass die Designanforderungen der Leiterplatte genauso gut sind wie das Chipdesign.

Ein typischer PCB-Design Der Prozess umfasst die folgenden Schritte:

Die ersten drei Schritte nehmen die meiste Zeit in Anspruch, da die Schaltplanenprüfung ein manueller Vorgang ist. Stellen Sie sich ein SoC Board mit 1000 oder mehr Anschlüssen vor. Jede Verbindung manuell zu überprüfen ist eine mühsame Aufgabe. Tatsächlich ist es fast unmöglich, jede Verbindung zu überprüfen, was Probleme in der Endplatine verursachen kann, wie falsche Verbindungen, schwimmende Knoten usw.

Die schematische Erfassungsstufe ist normalerweise mit folgenden Arten von Problemen konfrontiert:

Unterstrichfehler: zum Beispiel APLLVDD und APLL_VDD

Fallfrage: wie VDDE und vdde

Rechtschreibfehler

Signalkurzschlussproblem

es gibt mehr......

Um diese Fehler zu vermeiden, sollte es eine Möglichkeit geben, den kompletten Schaltplan innerhalb weniger Sekunden zu überprüfen. Dieses Verfahren kann durch Schaltplansimulation realisiert werden, was im aktuellen Leiterplattendesignprozess selten ist. Die schematische Simulation ermöglicht es Ihnen, die endgültige Ausgabe auf dem gewünschten Knoten anzuzeigen, so dass es automatisch auf alle Verbindungsprobleme überprüft.

Das Folgende wird anhand von Projektbeispielen erläutert. Betrachten Sie ein typisches Leiterplattenblockdiagramm:

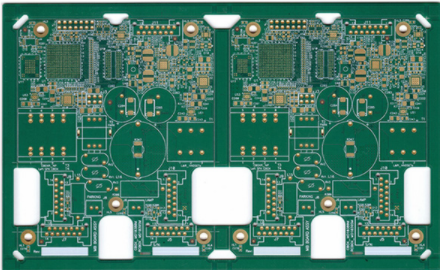

Wie reduziert man PCB-Design Fehler und verbessern Sie Ihre Design-Effizienz in Leiterplattenlayout

In einem komplexen Leiterplattendesign kann es Tausende von digitalen Verbindungen geben, und nur wenige Änderungen können viel Zeit für die Inspektion verschwenden.

Schematische Simulation kann nicht nur Designzeit sparen, sondern auch die Qualität der Leiterplatte verbessern und die allgemeine Prozesseffizienz verbessern.

Ein typischer Prüfling hat folgende Signale:

Nach einiger Voreinstellung verfügt das zu testende Gerät über verschiedene Signale und verschiedene Module zur Signaleinstellung, wie Spannungsregler, Operationsverstärker usw. Betrachten Sie ein Beispiel für ein Leistungssignal, das von einem Spannungsregler erhalten wird:

Um die Verbindung zu verifizieren und eine Gesamtinspektion durchzuführen, wurde eine schematische Simulation verwendet. Die schematische Simulation umfasst die Erstellung von Schaltplänen, die Erstellung von Testplattformen und die Simulation.

Während der Erstellung der Testplattform wird das Reizsignal an den notwendigen Eingang gesendet, und dann wird der Ausgang am Signalpunkt von Interesse beobachtet.

Der obige Prozess kann realisiert werden, indem die Sonde mit dem zu beobachtenden Knoten verbunden wird. Die Knotenspannung und Wellenform können anzeigen, ob Fehler im Schaltplan vorliegen. Alle Signalverbindungen werden automatisch geprüft.

Wie lassen Sie Leiterplattenhersteller Fehler in PCB-Design und ihre Konstruktionseffizienz verbessern

Werfen wir einen Blick, die erkannten Knoten und Spannungen sind deutlich sichtbar:

So können wir mit Hilfe der Simulation die Ergebnisse direkt beobachten und bestätigen, dass das schematische Diagramm der Leiterplatte korrekt ist. Darüber hinaus ist es möglich, Designänderungen durch sorgfältige Anpassung von Reizsignalen oder Bauteilwerten zu untersuchen. Daher kann die schematische Simulation viel Zeit für Leiterplattendesign- und Inspektionspersonal sparen und die Möglichkeit der Konstruktionsgenauigkeit erhöhen.