PCIカードの配線はより洗練されている, PCIシグナルの特性によって決定される. 従来の高周波デジタル PCB回路 基板 デザイン, 我々は常に信号の反射を避けるために努力する, オーバーシュート, リンギング, インピーダンス不整合による非単調現象. しかし, PCI信号は、信号反射の原理を使用して物理信号を送信する, 大きなオーバーシュートのような副作用を回避しようとしている間、信号反射の妥当な使用をするために, リンギングと非単調性, PCI SIGはPCI仕様でPCB物理実現に関するいくつかの規定をしました.

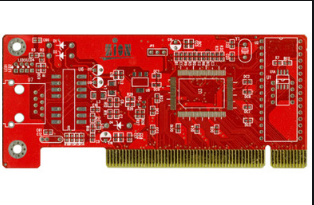

PCI - SIGはAの使用を推奨する4層PCBPCIカード用ボード. PCI - SIGによって指定されたPCIコネクタの信号分配も、4層基板配線の便宜のために最適化される. PCI - SIGはまた、PCIコントローラのピン分配のための推奨された回路図を作りました. 事実上, AMCCなどのPCIコントローラメーカー, PLX, そして、オックスフォードもこの推薦を実行しました. この推奨ピン配布の下で, 二層使用. PCBボードは配線にとても便利です, しかし、PCIカードシステムハードウェアが非常に複雑で、複数の電力分割レベル, 多層PCBを有する方がよい.

PCIカード上の任意のPCI信号は、1つの負荷(プルアップ抵抗器に接続することもできない)に接続することができます。CLK、RST、INTA DELIGHI ~ IND DEMUNHI、JTAGを除くと、ゴールデンフィンガーとカードソケットの接触点からのロードピンまでのすべてのピンは、1.5インチより大きくてはならないCLK信号の長さは2.5±0.1インチであり、この長さは少し長いので、多くの場合、長さ要件を満たすために迂回される必要がある。これは、しばしばPCIカード上のCLKの蛇行のトレースを参照してください理由です残りのピンには特別規制はない。多層PCBを使用する場合、信号トレースは異なるパワーレベル(少なくとも分割電力レベルを有する層はPCBの反対側にあるべきである)を交差させるべきではない。その理由は、PCIカードのA側の全ての金フィンガーが、しばしば信号がホールを介してB側(コンポーネント側)に行く理由を理解する理由である。

各PCI信号の特性インピーダンスは60〜100オームであり、負荷容量は10 pFを超えてはならない。ICのIOパッドは- 3.5 Vアンダーシュートと+ 7.1 Vの信号オーバーシュートに耐えることができるはずです。AMCC、PLX、オックスフォードなどのPCIコントローラメーカーでは、コントローラICはこれらの規則を満たしており、ユーザはそれを考慮する必要がない。しかし、PCIコントローラを実装するためにCPLD / FPGAを使用する場合、使用するモデルがこれらの規則を満たしているかどうかを考慮する必要があります。CPLA / FPGAメーカーは、AlteraとXilinxのように、CPLD / FPGAがPCI信号仕様と互換性があるかどうか、彼らのデータマニュアルではっきりと述べます。

井戸, 普通の32ビット33 MHz PCIカードの配線は比較的簡単です, 主に長さ要件を満たす. 事実上, あなたが厳密に配線要件に従っていないならば, 一般に問題はない, マザーボードチップセットによって, 信号互換性問題が発生すると, PCIカードのハードウェアデバッギングはPCB回路 基板設計.