PCI 카드는 PCI 신호의 특성에 따라 더 정교하게 배선됩니다.전통적인 고주파 디지털 PCB 회로 기판 설계에서 우리는 항상 임피던스 미스매치로 인한 신호 반사, 과충격, 벨 진동 및 비단조로운 현상을 피하기 위해 노력합니다.그러나 PCI 신호는 신호 반사의 원리를 이용하여 물리적 신호를 전송하며, 신호 반사를 합리적으로 이용하고, 동시에 과충, 진동 벨, 비단조 등 부작용을 최대한 피하기 위해 PCI-SIG는 PCI 규범에서 PCB 물리적 실현에 대해 일부 규정을 내렸다.

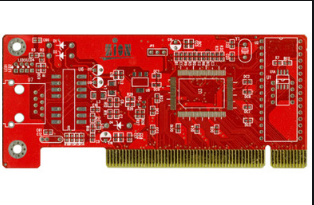

PCI-SIG는 PCI 카드에 4 레이어 PCB 보드를 사용하는 것이 좋습니다.PCI-SIG가 지정한 PCI 커넥터의 신호 분포도 최적화되어 4 레이어 보드 케이블 연결이 용이합니다.PCI-SIG는 PCI 컨트롤러의 핀 분포를 위한 권장 도식도 제작했다.실제로 AMCC, PLX 및 OXFORD와 같은 PCI 컨트롤러 제조업체도이 권장 사항을 구현했습니다.제안된 핀 분포에서 두 레이어가 사용됩니다.PCB 보드는 실제로 케이블 연결이 매우 쉽지만 PCI 카드 시스템 하드웨어가 매우 복잡하고 여러 전력 할당 수준이 필요한 경우 다중 레이어 PCB를 사용하는 것이 좋습니다.

PCI 카드의 모든 PCI 신호는 업로드 저항기를 포함하여 하나의 로드에만 연결할 수 있습니다.CLK, RST, INTA#~INTD#, JTAG 등의 핀을 제외하고 금손가락과 카드 콘센트의 접촉점에서 부하단까지의 모든 핀은 1.5인치 이상이어야 합니다.CLK 신호의 길이는 2.5 + / -0.1인치이며, 이 길이는 약간 길기 때문에 많은 경우 길이 요구 사항을 충족하기 위해 사방으로 배선해야 합니다.그래서 PCI 카드에서 CLK의 뱀 모양 궤적을 자주 볼 수 있습니다.나머지 핀에 대해서는 특별한 규정이 없다.다층 PCB를 사용할 때 신호 흔적선은 서로 다른 전력 레벨을 뛰어넘어서는 안 된다. (적어도 분열 전력 레벨을 가진 층은 PCB의 반대편에 있어야 한다.) 이것이 바로 우리가 PCI 카드 a측의 모든 금손가락이 나타나는 원인이다. 신호는 항상 구멍을 통해 B측(어셈블리측)에 도달하는 원인이다.

각 PCI 신호의 특성 임피던스는 60-100옴이며 부하 용량은 10pf를 초과할 수 없습니다.IC의 IO 용접판은 -3.5V의 하향과 +7.1V의 신호 과충을 견딜 수 있어야 한다.AMCC, PLX, OXFORD와 같은 PCI 컨트롤러 제조업체의 경우 컨트롤러 IC가 이러한 규정을 준수하므로 사용자는 고려할 필요가 없습니다. 그러나 CPLD/FPGA를 사용하여 PCI 컨트롤러를 구현하는 경우 사용 모델이 이러한 규정을 준수하는지 고려해야 합니다.Altera 및 Xilinx와 같은 CPLD/FPGA 제조업체는 데이터 매뉴얼에 CPLD/FFPGA가 PCI 신호 사양과 호환되는지 여부를 명시할 것입니다.

음, 일반 32비트 33MHz PCI 카드의 배선은 상대적으로 간단하며, 주로 길이 요구를 만족시키기 위한 것이다.사실, 케이블 연결 요구 사항을 엄격히 따르지 않으면 일반적으로 문제가 발생하지 않지만 마더보드 칩셋에 따라 신호 호환성 문제가 발생하면 PCI 카드의 하드웨어 디버깅은 PCB 회로 설계에서 가장 고통스러운 경험이 될 것입니다.