Offer reply within 30 minutes, 1-hour engineering response, 24-hour technical support, save customer waiting time, shorten product development and production cycle from all aspects, save product launch time, and quickly occupy the market for your products.

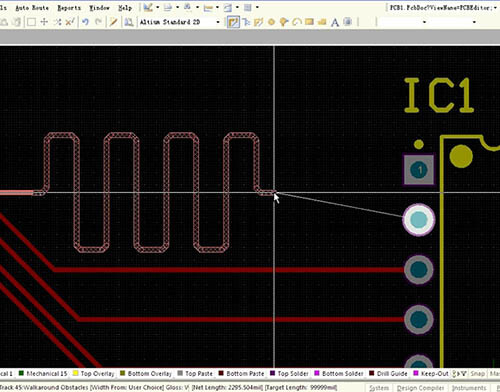

Over ten years of development, we grow year on year to add technology and capacity. PCB technology from the standard PCB to RF circuit, microwave circuit board, Multilayer PCB, Rigid-flexible PCB, HDI PCB, IC substrate, IC test board, PCBA assembly.

The support and trust of our partners are the driving force for our progress. We are looking for a win-win business with our customers. There is no small or big customer in our company culture. Always doing our best to provide excellent service is our goal.

Wide selection of PCB material suppliers, such as Isola, Panasonic, TUC, ITEQ, Shengyi, KB, Rogers, Arlon, Taconic, Doosan, Mitsubishi Gas, DuPont, etc.

Stock materials: FR408, 370HR, TU872, RO4350B, RO4003C, RT5880, RO3010, RO3003, RF35, TLY-5, Megtron4, Megtron6, S1000-2, IT180, F4BM PCB prototype material.

Support FR-4 PCB, Multilayer circuit board, HDI PCB, Ceramic PCB, PTFE printed circuit board, Hybrid circuit, Teflon PCB, RF PCB, Rogers PCB. Advanced PCB ERP tracking management system leads the industry in delivery time, PCB On-time delivery rate above 95%.

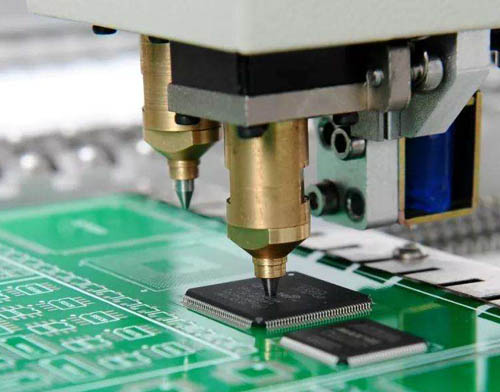

Strict quality control system guaranteed us one of the most experienced printed circuit board manufacturers in China with over ten years. PCB factory of iPCB professional fabrication PCB prototype, IPC Class III standard can be selected based on customer requirements.

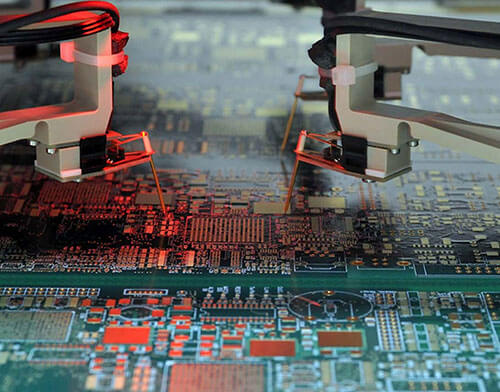

iPCB has successively cooperated with more than 10,000 high-tech R&D, manufacturing, and service companies worldwide. Its products are used in communications circuits, industrial control circuit board, rail transit PCB board, medical electronics PCB, computers PCB, semiconductors substrate, automotive electronics PCB, and other printed circuit board fields. iPCB also supplies one-stop PCB - PCBA assembly manufacturing, with resources covering more than 60 worldwide Countries.

2025-02-27

2021-12-13