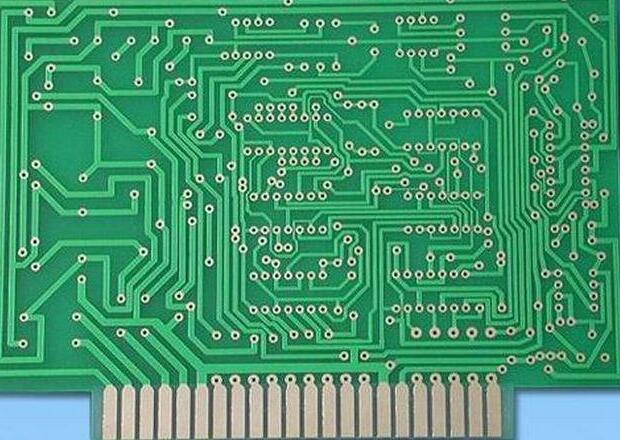

Warum müssen wir serpentine isometrisches Design im PCB-Design machen

In PCB-Design, Gleichlange Spuren sind hauptsächlich für einige Hochgeschwindigkeits-Parallelbusse bestimmt.

Da diese Art von Parallelbus oft mehrere Datensignale auf der Grundlage der gleichen Uhr abgetastet hat, each clock cycle may need to be sampled twice (DDRSDRAM) or even 4 times. Mit zunehmender Betriebsfrequenz des Chips, Die Signalübertragungsverzögerung beeinflusst das Timing Der Anteil wird größer und größer. In order to ensure that the value of all signals can be collected correctly at the data sampling point (the rising or falling edge of the clock), die Verzögerung der Signalübertragung muss kontrolliert werden. Der Zweck von gleichlangen Leiterbahnen ist es, die Differenz in der Übertragungsverzögerung aller relevanten Signale auf dem PCB.

Das effektive Einrichtungs- und Wartungsfenster von Hochgeschwindigkeitssignalen ist relativ klein. Damit Daten und Steuersignale in das effektive Fenster fallen, der Unterschied in der Spurlänge zwischen den Daten, Uhr oder Daten, und zwischen Steuersignalen ist sehr klein. Die spezifische zulässige Abweichung kann durch Berechnung der Zeitverzögerung ermittelt werden.

In der Tat, im Allgemeinen, Sequenzielle Logiksignale müssen die Rüstzeit und Haltezeit erfüllen und einen gewissen Spielraum haben. Solange diese Bedingung erfüllt ist, das Signal darf nicht unbedingt gleich lang sein.

Allerdings, the actual situation is that for high-speed signals (such as DDR2, DDR3, FSB), it is impossible to know whether the timing meets the setup time and hold time requirements during the design (there are too many influencing factors, including the internal wiring and capacitance of the chip). Der durch die Last verursachte Verzögerungsunterschied muss berücksichtigt werden, it is difficult to estimate the actual value through calculation), a controllable delay device must be set inside the chip (the delay is controlled by the register), und dann wird der Wert des Registers gescannt, um verschiedene Verzögerungen auszuprobieren. And by observing the signal (look at the waveform directly, and measure the setup and hold time) to determine the delay value to meet the setup time and hold time requirements. Allerdings, Der gleiche Signaltyp wird in der Regel nur für eine oder einige der Signalleitungen beobachtet. Damit alle Signale den zeitlichen Anforderungen entsprechen, die gleiche Art der Signalverdrahtung muss streng gleich lang sein.

We are not an agent

Our factory is located in China. Seit Jahrzehnten, Shenzhen has been known as the world's electronics R&D and manufacturing center. Unsere Fabrik und Website werden von der chinesischen Regierung genehmigt, So können Sie die Zwischenhändler überspringen und Produkte auf unserer Website mit Vertrauen kaufen. Weil wir eine direkte Fabrik sind, this is the reason why 100% of our old customers continue to purchase on iPCB.

No minimum requirements

You can order as little as 1 PCB von uns. Wir werden Sie nicht zwingen, Dinge zu kaufen, die Sie wirklich nicht brauchen, um Geld zu sparen.

Free DFM

Before you pay in the most timely manner, Alle Ihre Aufträge werden von unserem gut ausgebildeten Fach- und Technikpersonal kostenlos überprüft..