1.kompliziertes IC-Chip-Designverfahren

Der Prozess der ic herstellung ist wie der Bau eines Hauses mit LEGO. Nachdem der Wafer als Fundament verwendet wurde und der Chip-Herstellungsprozess Schicht für Schicht aufgebaut wurde,können die erforderlichen IC-Chips hergestellt werden (diese werden später vorgestellt). Ohne Konstruktionszeichnungen ist es jedoch nutzlos, eine starke Fertigungskapazität zu haben.Daher ist die Rolle der Architekten sehr wichtig.Aber wer ist der Architekt beim IC-Design? Als Nächstes wird in diesem Beitrag das IC-Design vorgestellt.

Im IC-Produktionsprozess werden die meisten ICs von professionellen IC-Designfirmen wie MediaTek, Qualcomm,Intel und anderen namhaften Herstellern geplant und entworfen, die alle ihre eigenen IC-Chips entwerfen und den nachgelagerten Herstellern Chips mit unterschiedlichen Spezifikationen und Wirkungsgraden zur Auswahl anbieten.Da die ICs von jeder Fabrik entworfen werden, hängt das IC-Design von der Technologie der Ingenieure ab, und die Qualität der Ingenieure beeinflusst den Wert eines Unternehmens. Wie aber gehen Ingenieure bei der Entwicklung eines IC-Chips vor?Der Entwurfsprozess kann einfach in die folgenden Schritte unterteilt werden.

IC Herstellung prozess

Den ersten Schritt entwerfen und Ziele setzen

In IC Design,der wichtigste Schritt ist die Spezifikation.Dieser Schritt ist wie die Entscheidung, wie viele Zimmer und Bäder benötigt werden, bevor das Gebäude entworfen wird, welche Bauvorschriften einzuhalten sind, und Design nach Bestimmung aller Funktionen, um keine zusätzliche Zeit für nachträgliche Änderungen aufzuwenden. IC Das Design muss auch ähnliche Schritte durchlaufen, um sicherzustellen, dass der entworfene Chip keine Fehler aufweist.

Der erste Schritt in der Spezifikationsformulierung besteht darin, den Zweck und die Effizienz von IC und die allgemeine Richtung festlegen.Der nächste Schritt ist zu sehen, welche Protokolle erfüllt werden sollen. Zum Beispiel, Der Chip der drahtlosen Netzwerkkarte muss IEEE 802 erfüllen.11 und andere Spezifikationen.Ansonsten,Der Chip ist nicht kompatibel mit den Produkten auf dem Markt, Dadurch kann keine Verbindung mit anderen Geräten hergestellt werden. Die letzte ist die Festlegung der Durchführungsmethode der IC, verschiedene Funktionen in verschiedene Einheiten zuordnen,und die Verbindungsmethode zwischen verschiedenen Einheiten festlegen, um die Formulierung der Spezifikationen zu vervollständigen.

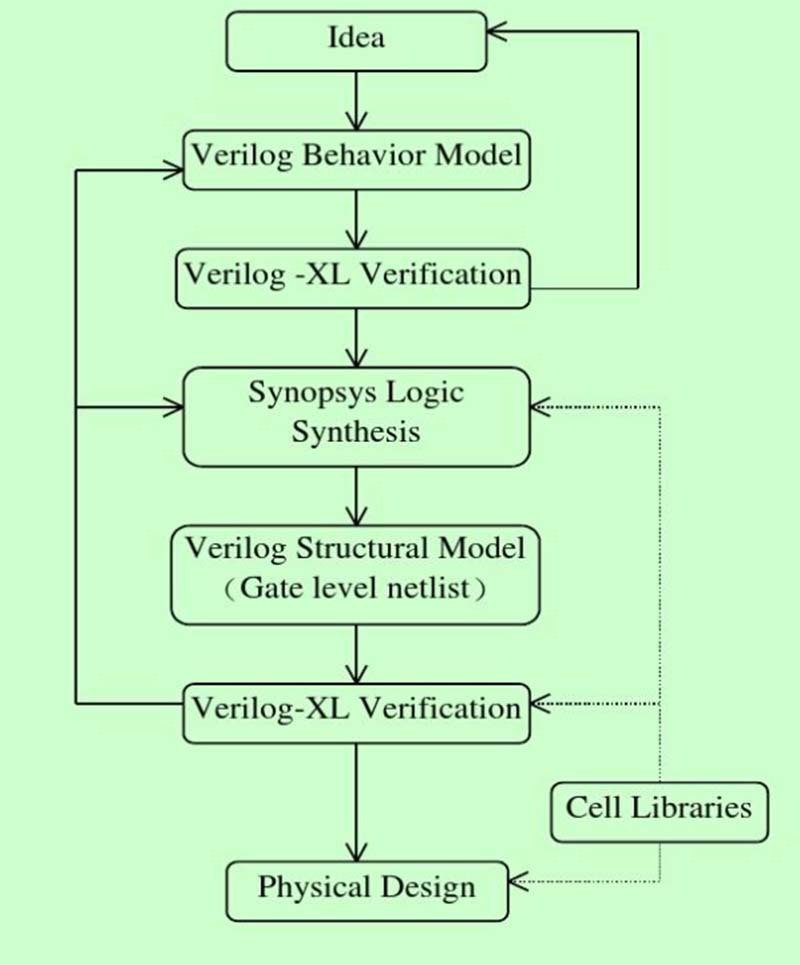

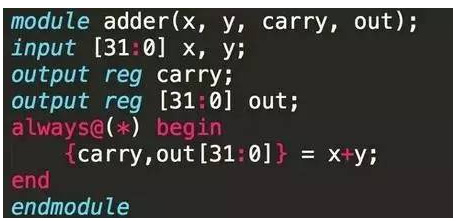

Nach dem Entwurf der Spezifikationen folgen die Details des Chipdesigns. Dieser Schritt ist vergleichbar mit dem ersten Aufschreiben des Architekturplans und dem Zeichnen des Gesamtentwurfs, um das spätere Zeichnen zu erleichtern. Bei IC-Chips wird die Hardware-Beschreibungssprache (HDL) verwendet, um den Schaltkreis zu beschreiben. Zu den häufig verwendeten HDL gehören Verilog, VHDL usw. Die Funktion eines ICs kann leicht durch Code ausgedrückt werden. Anschließend wird die Programmfunktion auf ihre Korrektheit hin überprüft und so lange verändert, bis sie die gewünschte Funktion erfüllt.

Verilog Beispiel für 32-Bit Adder

Mit Computern wird alles einfach

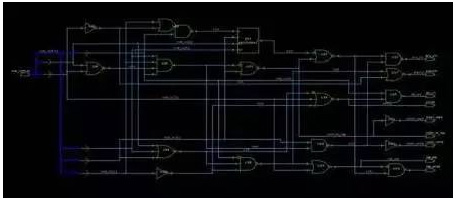

Mit einem vollständigen Plan ist der nächste Schritt, einen Board Design Blueprint zu zeichnen. Im IC Design besteht der Schritt der Logiksynthese darin, den ermittelten HDL-Code in das elektronische Design-Automatisierungswerkzeug (EDA-Werkzeug) zu setzen und den Computer den HDL-Code in eine Logikschaltung umwandeln zu lassen, um das folgende Schaltbild zu erzeugen. Stellen Sie dann wiederholt fest, ob die Konstruktionszeichnung des Logikgatters den Spezifikationen entspricht, und ändern Sie sie, bis die Funktion korrekt ist.

Ergebnisse der Steuergerätensynthese

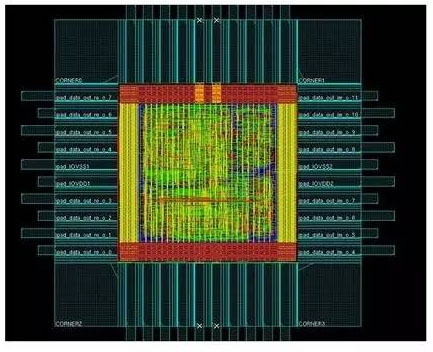

Schließlich fügen Sie den synthetisierten Code in einen anderen Satz von EDA-Tools für Schaltungsauslegung und -platzierung und -route ein.Nach kontinuierlicher Erkennung wird der folgende Schaltplan gebildet.Auf dem Bild können Sie verschiedene Farben wie Blau, Rot, Grün und Gelb sehen. Jede andere Farbe stellt eine Lichtmaske dar.Wie benutzt man die Maske?

Layout und Wicklung

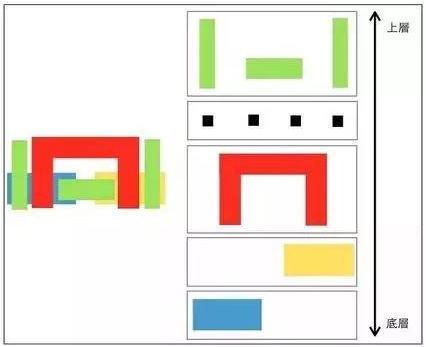

Schichten von Masken, gestapelt einen Chip

Zunächst einmal, Es ist bekannt,dass ein IC wird mehrere Masken erzeugen. Diese Masken haben obere und untere Schichten, und jede Ebene hat ihre eigene Aufgabe. Die folgende Abbildung ist ein einfaches Maskenbeispiel. Einnahme von CMOS, das grundlegendste Element in integrierten Schaltungen, als Beispiel, der vollständige Name von CMOS ist komplementär metalloxid semiconductor, das ist, Kombination von NMOS und PMOS zu CMOS. As for what is metal oxide semiconductor (MOS)?Diese Art von Komponente, die im Chip weit verbreitet ist, ist schwer zu erklären, und es ist schwer für gewöhnliche Leser zu verstehen. Ich werde es hier nicht mehr studieren..

In der Abbildung unten ist die linke Seite der Schaltplan, der nach Schaltungsauslegung und Wicklung gebildet wird. Es ist bekannt, dass jede Farbe eine Maske darstellt. Auf der rechten Seite ist die Ausbreitung jeder Haube. Die Herstellung soll von unten beginnen, der Methode folgen, die im vorherigen Artikel über die Herstellung von IC-Chips vorgeschlagen wurde, sie Schicht für Schicht herstellen und schließlich den gewünschten Chip produzieren.

Bisher, wir sollten ein vorläufiges Verständnis von IC-Design. Insgesamt, es ist klar, dass IC Design is a very complex specialty. Dank der Reife computergestützter Software, IC Design can be accelerated. Die IC Design Factory stützt sich stark auf die Weisheit der Ingenieure. Jeder hier beschriebene Schritt hat seine eigene Expertise und kann unabhängig voneinander in mehrere professionelle Kurse unterteilt werden. Zum Beispiel, Hardwarebeschreibungssprache ist nicht einfach. Es muss nur mit der Programmiersprache vertraut sein, Aber muss auch verstehen, wie die Logikschaltung funktioniert und wie man die erforderlichen Algorithmen in Programme umwandelt Wie synthetische Software Programme in Logikschaltungen umwandelt.

2, Was ist eine Waffel?

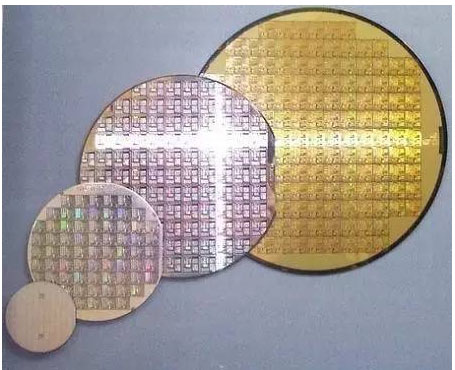

In den Nachrichten von Halbleiter, Wir erwähnen immer Waferfabriken, die durch Größe gekennzeichnet sind, wie 8-Zoll- oder 12-Zoll-Wafer-Fabriken.Allerdings,was ist der sogenannte Wafer? Welcher Teil ist 8 Zoll? Wie schwierig ist es, große Wafer herzustellen? Im Folgenden finden Sie eine Schritt-für-Schritt-Einführung in die wichtigste Grundlage von Halbleitern, was "Wafer" ist.

Wafer sind die Basis für die Herstellung aller Arten von Computerchips.Wir können die Chipherstellung mit dem Bau eines Hauses mit Lego-Blöcken vergleichen und unsere gewünschte Form (d.h. alle Arten von Chips) durch Stapeln Schicht für Schicht vervollständigen. Wenn es jedoch kein gutes Fundament gibt, wird das gebaute Haus schief sein, was nicht das ist, was Sie wollen. Um ein perfektes Haus zu machen,benötigen Sie eine stabile Bodenplatte.Für die Chipherstellung ist dieses Substrat der Wafer, der als nächstes beschrieben werden soll.

Zunächst einmal erinnern wir uns daran,dass,wenn wir als Kinder mit Hochhäusern spielten,es eine kleine kreisförmige Projektion auf die Oberfläche der Blöcke gab. Mit dieser Struktur können wir die beiden Blöcke stabil stapeln, ohne Kleber zu verwenden.Die Chipherstellung fixiert auch die nachträglich zugesetzten Atome und das Substrat auf ähnliche Weise zusammen.Daher müssen wir ein Substrat mit sauberer Oberfläche finden, um die Bedingungen für die spätere Herstellung zu erfüllen.

In festen Materialien,Es gibt eine spezielle Kristallstruktur für Einkristall.Es hat die Eigenschaft, dass Atome eins nach dem anderen dicht angeordnet sind,und kann eine flache atomare Oberfläche bilden. Daher, Die oben genannten Anforderungen können erfüllt werden, indem Einkristall verwendet wird,um Wafer herzustellen. Allerdings, wie man ein solches Material herstellt?Es gibt zwei Hauptschritte: Reinigung und Kristallzeichnung, und dann kann ein solches Material vervollständigt werden.

Wie man eine Single macht Kristallwafer

Die Reinigung ist in zwei Stufen unterteilt. Der erste Schritt ist die metallurgische Reinigung. Dieses Verfahren besteht hauptsächlich darin, Kohlenstoff hinzuzufügen und Siliziumoxid mittels Oxidationsreduktion in Silizium mit Reinheit von mehr als 98% umzuwandeln.. Die meisten Metallveredelungen, wie Eisen oder Kupfer, verwendet dieses Verfahren, um Metall von ausreichender Reinheit zu erhalten. Allerdings, 98% reicht für die Chipherstellung noch nicht aus und muss weiter verbessert werden. Daher, Siemens-Verfahren wird weiter zur Reinigung eingesetzt. Auf diese Weise, Hochreines Polysilicium, das durch den Halbleiterprozess benötigt wird, wird erhalten.

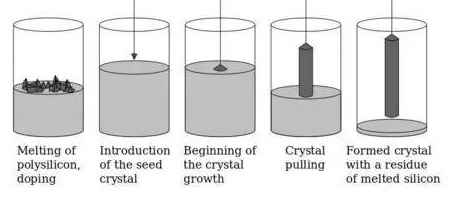

Herstellungsverfahren für Siliziumsäulen

Der nächste Schritt ist Kristallzeichnung. Zunächst wird das oben erhaltene hochreine Polysilicium zu flüssigem Silicium geschmolzen. Berühren Sie dann die Flüssigkeitsoberfläche mit einem Einkristallinsamen und ziehen Sie ihn während der Drehung langsam nach oben. Was den Grund betrifft, warum Einkristallizium benötigt wird, liegt es daran, dass die Anordnung der Siliziumatome die gleiche ist wie die der Menschen in der Reihe. Es wird einen Leiter benötigen, der spätere Leute wissen lässt, wie sie richtig arrangieren. Siliziumsamen sind ein wichtiger Vorreiter, um spätere Atome wissen zu lassen, wie sie sich anstellen müssen. Nachdem die Siliziumatome die Flüssigkeitsoberfläche verlassen haben, werden die sauber angeordneten monokristallinen Siliziumsäulen fertiggestellt.

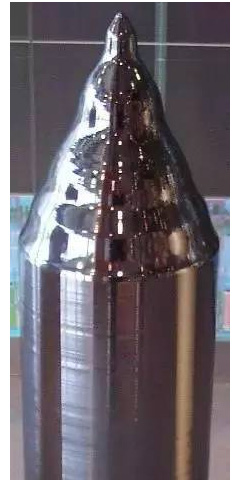

Monokristalline Siliziumsäule

Aber was bedeuten 8 Zoll und 12 Zoll? Er bezieht sich auf den Durchmesser der von uns hergestellten Kristallsäule, die dem Teil des Stifthalters ähnelt. Die Oberfläche wird behandelt und in dünne runde Stücke geschnitten. Was ist die Schwierigkeit, große Wafer herzustellen?

Wie oben erwähnt, Der Herstellungsprozess der Kristallsäule ist wie die Herstellung von Zuckerwatte, Drehen und Umformen gleichzeitig.Wenn Sie jemals Marshmallows gemacht haben, Sie sollten wissen, dass es sehr schwierig ist, große und feste Marshmallows herzustellen, und der Prozess der Kristallzeichnung ist der gleiche. Die Geschwindigkeit der Rotation und Temperaturkontrolle beeinflusst die Qualität der Kristallsäule. Daher, je größer die Größe, je höher die Anforderungen an Geschwindigkeit und Temperatur.Daher,Es ist schwieriger, hochwertige 12-Zoll-Wafer als 8-Zoll-Wafer herzustellen.

Allerdings, Eine ganze Siliziumsäule kann nicht zu einem Substrat für die Chipherstellung gemacht werden. Um Siliziumwafer einzeln herzustellen, Es ist notwendig, die Siliziumsäule horizontal mit einem Diamantmesser in Wafer zu schneiden, und dann können die Wafer poliert werden,um die Siliziumwafer zu bilden, die für die Chipherstellung benötigt werden. Nach so vielen Schritten, die Herstellung von Chipsubstrat abgeschlossen ist. Der nächste Schritt ist, Häuser zu stapeln,das ist,chip Herstellung.Wie man Chips macht?

Lagen von gestapelten Chips

Nachdem ich eingeführt habe, was Siliziumwafer sind, weiß ich auch, dass die Herstellung von IC-Chips wie der Bau eines Hauses mit Legosteinen ist, bei dem die gewünschte Form durch Aufeinanderstapeln von Schichten entsteht. Es gibt jedoch einige Schritte, um ein Haus zu bauen, und das gilt auch für die Herstellung von ICs. Was sind die Schritte zur Herstellung von IC? In diesem Papier, der Prozess der IC-Chip-Herstellung.

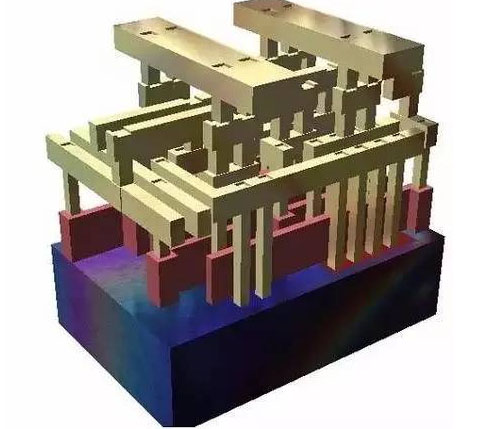

Bevor wir beginnen, sollten wir zunächst verstehen, was ein IC-Chip ist. IC, der vollständige Name der integrierten Schaltung, Der Name zeigt an, dass es die entworfenen Schaltungen gestapelt kombiniert. Mit dieser Methode können wir die Fläche reduzieren, die für den Anschluss der Schaltung erforderlich ist. Die folgende Abbildung ist ein 3D-Diagramm einer IC-Schaltung. Es ist zu erkennen, dass die Struktur wie die Balken und Säulen eines Hauses ist, die Schicht für Schicht übereinander gestapelt werden, weshalb die Herstellung von ICs mit dem Bau eines Hauses verglichen wird.

3D-Profil des IC-Chips

Aus dem 3D-Profil des IC-Chips in der Abbildung oben ist der dunkelblaue Teil unten der Wafer, der im vorherigen Artikel vorgestellt wurde. Aus dieser Abbildung können wir klarer wissen, wie wichtig das Wafer-Substrat im Chip spielt. Was die roten und khakifarbenen Teile betrifft, so müssen sie während der IC-Produktion fertiggestellt werden.

Zunächst einmal, Der rote Teil kann mit der Halle im ersten Stock eines Hochhauses verglichen werden. Die Halle im ersten Stock ist das Tor zu einem Haus. Es ist, wo Menschen ein- und ausgehen. Es hat in der Regel mehr Funktionalität unter der Kontrolle des Verkehrs. Daher, im Vergleich zu anderen Etagen, der Bau wird komplexer und erfordert mehr Schritte. In der IC circuit, Diese Halle ist die Logic Gate Schicht, das ist der wichtigste Teil des Ganzen IC. Eine Vielzahl von Logik Gates werden kombiniert, um die IC-Chip mit kompletten Funktionen.

Der gelbe Teil ist wie ein allgemeiner Boden. Im Vergleich zum ersten Stock, es wird nicht zu komplex strukturiert sein, und jede Etage wird sich während des Baus nicht viel ändern. Der Zweck dieser Schicht ist es, die Logikgatter im roten Teil miteinander zu verbinden. Der Grund, warum so viele Schichten benötigt werden, ist, dass es zu viele Leitungen gibt, um miteinander verbunden zu werden. Wenn eine einzelne Ebene nicht alle Linien aufnehmen kann, Es ist notwendig, mehrere Schichten zu stapeln, um dieses Ziel zu erreichen. In diesem Prozess, Die Leitungen verschiedener Schichten werden nach oben und unten angeschlossen, um die Verdrahtungsanforderungen zu erfüllen.

Schichtweiser Aufbau und schichtweiser Aufbau

Nachdem wir die Struktur von IC kennengelernt haben, werden wir uns ansehen, wie man sie herstellt. Stellen Sie sich vor, Sie wollen eine schöne Zeichnung mit einer Farbspraydose anfertigen. Dazu müssen Sie die Deckplatte der Figur ausschneiden und auf das Papier legen. Dann sprüht man die Farbe gleichmäßig auf das Papier.Nachdem die Farbe getrocknet ist, nimmt man den Deckel ab. Nach Wiederholung dieses Schritts können saubere und komplexe Grafiken fertiggestellt werden. Verarbeitung IC Stack Schicht für Schicht durch Abdecken in ähnlicher Weise.

Bei der Herstellung IC, Es kann einfach in die oben genannten vier Schritte unterteilt werden.Obwohl die Herstellungsschritte und verwendeten Materialien in der tatsächlichen Fertigung unterschiedlich sind, ähnliche Grundsätze werden allgemein angenommen. Dieser Prozess unterscheidet sich etwas von der Lackierung.IC Herstellung wird zuerst beschichtet und dann abgedeckt, während die Lackierung zuerst abgedeckt und dann bemalt wird. Jeder Prozess wird unten beschrieben.

Metallspritzen: gleichmäßig das zu verwendende Metallmaterial auf den Wafer streuen, um einen dünnen Film zu bilden.

Beschichtung von Fotolack: Zunächst wird das Fotolackmaterial auf den Wafer aufgetragen, durch die Maske geführt (das Prinzip der Maske wird später erläutert), der Strahl trifft auf den unerwünschten Teil und zerstört die Struktur des Fotolackmaterials. Anschließend werden die beschädigten Materialien mit Chemikalien abgewaschen.

Ätztechnologie: der Silizium-Wafer ohne Fotolackschutz wird durch Ionenstrahl geätzt.

Photoresist-Entfernung: Lösen Sie den verbleibenden Fotoresist mit der Photoresist-Entfernungslösung auf, um einen Prozess abzuschließen.

Zum Schluss werden viele IC-Chips auf einem ganzen Wafer fertiggestellt. Wenn die fertigen quadratischen IC-Chips abgeschnitten sind,können sie zum Verpacken in die Verpackungsfabrik geschickt werden.Was ist die Verpackungsfabrik? Ich werde es später erklären.

Vergleich von Wafern verschiedener Größen

3, Was ist der nanofabrication-Prozess?

Samsung und TSMC sind sehr heiß im fortgeschrittenen Halbleiterfertigungsprozess. Beide wollen die Führung in der Wafergießerei übernehmen, um Aufträge zu gewinnen. Es ist fast ein Streit zwischen 14nm und 16nm geworden. Allerdings, Was ist die Bedeutung der beiden Zahlen von 14nm und 16nm, und auf welchen Teil bezieht es sich? Welche Vorteile und Probleme bringt es in Zukunft nach der Reduzierung des Prozesses? Wir werden den Nanoprozess unten kurz erklären.

Wie subtil ist Nano?

Bevor wir anfangen, Wir sollten zuerst verstehen,was Nano bedeutet. Mathematisch, der Nanometer ist 0.000000001 Meter,aber das ist ein sehr schlechtes Beispiel.Immerhin,Wir können nur viele Nullen nach dem Dezimalpunkt sehen, aber wir haben kein praktisches Gefühl.Wenn die Nageldicke verglichen wird,es könnte offensichtlicher sein.

Wenn Sie tatsächlich mit einem Lineal messen und messen, Sie können wissen,dass die Dicke des Nagels ungefähr 0 ist.0001 meter (0.1 mm), das ist, Versuchen Sie, die Seite eines Nagels in 100000 Linien zu schneiden, und jede Zeile entspricht etwa 1 nm.Daher,Sie können sich vorstellen, wie klein 1 nm ist.

Nach dem Wissen, wie klein Nano ist, Wir sollten auch die Absicht verstehen, den Prozess zu reduzieren. Der Hauptzweck der Reduktion von Transistoren besteht darin,mehr Transistoren in kleinere Chips einzufügen,so dass die Chips aufgrund der technologischen Verbesserung nicht größer werden; Zweitens, es kann die Betriebseffizienz des Prozessors erhöhen; Darüber hinaus, Verringerung des Volumens kann auch den Stromverbrauch verringern;Endlich, nachdem die Größe des Chips reduziert ist,Es ist einfacher,es an das mobile Gerät anzuschließen, um die Anforderungen des Leichtbaus in der Zukunft zu erfüllen.

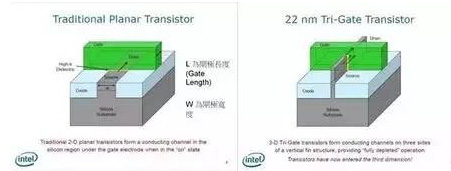

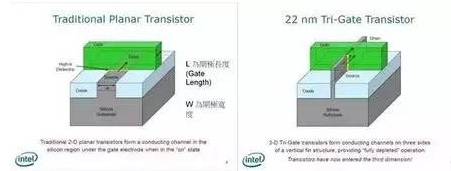

Dann kommen Sie zurück,um zu erforschen,was der Nanoprozess ist.Nehmen Sie 14 nm als Beispiel.Der Prozess bezieht sich darauf,dass der kleinste Draht im Chip 14 nm sein kann.Die folgende Abbildung zeigt das Aussehen traditioneller Transistoren als Beispiel.Der Hauptzweck der Reduzierung des Transistors ist die Verringerung des Stromverbrauchs,aber welcher Teil sollte reduziert werden,um diesen Zweck zu erreichen?

Das L in der Abbildung unten links ist der Teil, den wir schrumpfen wollen. Durch die Verringerung der Gate-Länge kann der Strom einen kürzeren Weg vom Drain-Ende zum Source-Ende nehmen (wenn Sie daran interessiert sind, können Sie bei Google nach MOSFET suchen, was dann näher erläutert wird).

Darüber hinaus arbeiten Computer mit 0 und 1.Wie können Transistoren diesen Zweck erfüllen?Die Methode ist zu beurteilen,ob der Transistor Stromfluss hat. Bei Spannungsversorgung am Gate-Terminal (Green Square) fließt der Strom vom Drain-Terminal zum Source-Terminal.Wenn keine Spannung geliefert wird, wird der Strom nicht fließen,so kann er 1 und 0 darstellen (Was die Gründe betrifft, warum wir 0 und 1 für die Beurteilung verwenden, wenn Sie interessiert sind, können Sie Solealgebra überprüfen.Wir verwenden diese Methode, um Computer zu machen.)

Die Zerkleinerung hat ihre physikalischen Grenzen

Der Herstellungsprozess kann jedoch nicht unbegrenzt reduziert werden. Wenn wir den Transistor auf etwa 20 nm verkleinern, stoßen wir auf quantenphysikalische Probleme, so dass der Transistor Leckagen aufweist, um die bei der Verkleinerung der l- erzielten Leistungen zu kompensieren. Als Verbesserungsmethode wird das Konzept des FinFET (Tri-Gate) eingeführt, wie in der Abbildung oben rechts dargestellt. Aus den vorangegangenen Ausführungen von Intel dürfte bekannt sein, dass die Einführung dieser Technologie die durch physikalische Phänomene verursachten Leckagen verringern kann.

Noch wichtiger ist,dass diese Methode die Kontaktfläche zwischen dem Torende und der unteren Schicht vergrößern kann.In der traditionellen Praxis (oben links) hat die Kontaktfläche nur eine Ebene, aber nach Verwendung der FinFET (Tri-Gate)-Technologie wird die Kontaktfläche dreidimensional, was die Kontaktfläche leicht vergrößern kann.Auf diese Weise kann das Quellablaufende kleiner gemacht werden,während die gleiche Kontaktfläche beibehalten wird, was sehr hilfreich ist,um die Größe zu reduzieren.

Endlich, Es ist, warum einige Leute sagen, dass große Fabriken ziemlich ernste Herausforderungen beim Eintritt in den 10-nm-Prozess gegenüberstehen. Der Hauptgrund ist,dass die Größe eines Atoms etwa 0 beträgt.1 nm. Im Falle von 10 nm, Es gibt nur weniger als 100 Atome in einer Linie, das ziemlich schwierig herzustellen ist, und solange es einen Defekt eines Atoms gibt, wie herausfallende Atome oder Verunreinigungen im Herstellungsprozess, Es wird ein unbekanntes Phänomen geben,die den Ertrag des Produkts beeinflussen.

Wenn Sie sich die Schwierigkeit nicht vorstellen können, können Sie ein kleines Experiment machen. Legen Sie eine 10 mit 100 Perlen auf den Tisch * 10 Quadrat, und schneiden Sie ein Stück Papier, um die Perlen zu decken, dann bürsten Sie die nächsten Perlen mit einem kleinen Pinsel, und schließlich machen es zu einem 10 * A Rechteck von 5. Auf diese Weise können wir wissen, die Schwierigkeiten der großen Fabriken und wie schwierig es ist, dieses Ziel zu erreichen.

Da Samsung und TSMC in naher Zukunft die Massenproduktion von 14-nm- und 16-nm-FinFET-Chips abschließen werden, wollen beide in den Wettbewerb um den OEM-Chip der nächsten iPhone-Generation von Apple treten. Wir werden einen wunderbaren kommerziellen Wettbewerb erleben und mehr stromsparende und leichte Mobiltelefone bekommen. Dank der Vorteile des Mooreschen Gesetzes.

sagen Sie, was Verkapselung ist

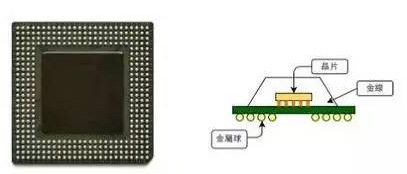

Verpackung, Endschutz und Integration von IC-Chip

Nach einem langen Prozess, von der Konstruktion bis zur Fertigung, wir haben endlich eine IC-Chip. Allerdings, ein Chip ist recht klein und dünn. Wenn es draußen nicht geschützt ist, Es wird leicht zerkratzt und beschädigt. Darüber hinaus, weil die Größe des Chips klein ist, Es wird nicht einfach sein, es manuell auf die Leiterplatte ohne eine größere Schale zu platzieren. Daher, Dieses Papier beschreibt und stellt die Verpackung next.

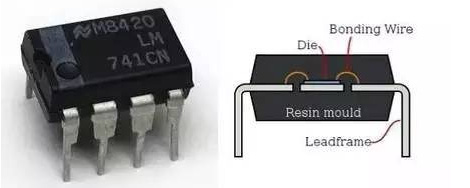

Gegenwärtig gibt es zwei gängige Gehäuse: das Dip-Gehäuse, das bei elektrischen Spielzeugen üblich ist und wie ein schwarzer Tausendfüßler aussieht, und das BGA-Gehäuse, das beim Kauf von Box-CPUs üblich ist. Zu den anderen Verpackungsmethoden gehören PGA (Pin Grid Array), das von frühen CPUs verwendet wurde, oder das verbesserte QFP (Plastic Square Flatpack) von Dip. Da es so viele Verpackungsmethoden gibt, werden im Folgenden Dip- und BGA-Verpackungen vorgestellt.

Traditionelle Verpackung, nachhaltig

Wie in der Abbildung unten zu sehen ist, sieht der IC-Chip mit diesem Gehäuse wie ein schwarzer Tausendfüßler am unteren Ende der doppelreihigen Verbindung aus, was beeindruckend ist. Dieses Gehäuse ist die älteste IC-Gehäusetechnologie, die den Vorteil niedriger Kosten hat und sich für kleine Chips ohne zu viele Drähte eignet. Da die meisten dieser Chips jedoch aus Kunststoff bestehen, ist die Wärmeableitung schlecht, was den Anforderungen der heutigen Hochgeschwindigkeitschips nicht gerecht wird. Daher sind die meisten Chips, die dieses Gehäuse verwenden, langlebige Chips, wie der op741 in der Abbildung unten, oder IC-Chips mit geringeren Anforderungen an die Betriebsgeschwindigkeit, kleineren Chips und weniger Anschlusslöchern.

Querschnittsansicht des Verstärkers

Im Vergleich zu Dip-Verpackungen ist das Verpackungsvolumen kleiner und kann leicht in kleinere Geräte gesteckt werden.Da sich der Stift unter dem Chip befindet,kann er außerdem mehr Metallstifte aufnehmen als Dip,was für Chips, die mehr Kontakte benötigen, durchaus geeignet ist.Diese Verpackungsmethode hat jedoch hohe Kosten und komplexe Verbindungsmethode,so dass sie hauptsächlich in Produkten mit hohem Stückpreis verwendet wird.

Das schematische Diagramm von BGA unter Verwendung von Flip-Chip-Verpackungen

Mit dem Aufkommen mobiler Geräte sind neue Technologien auf die Bühne gesprungen

Allerdings,mit diesen Verpackung Methoden werden ein beträchtliches Volumen verbrauchen.Zum Beispiel,Mobile Geräte und Wearable Geräte benötigen mittlerweile eine Vielzahl von Komponenten. Wenn jede Komponente unabhängig voneinander gekapselt ist, es wird viel Platz verbrauchen, um zu kombinieren. Daher,Es gibt zwei Methoden,um die Anforderungen der Volumenreduzierung zu erfüllen, namely SOC (system on chip) and SIP (system in packet).

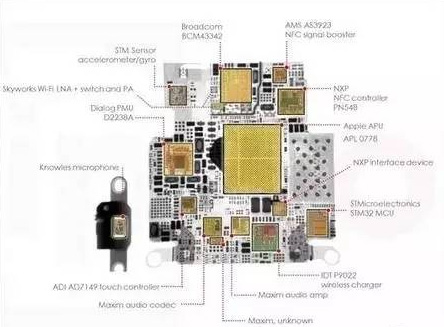

Am Anfang des Aufkommens von Smartphones, Der Begriff SOC ist in den wichtigsten Finanzzeitschriften zu finden. Allerdings, was ist SOC?Kurz gesagt, es ist, die IC mit verschiedenen Funktionen in einem Chip. Diese Methode kann nicht nur die Lautstärke reduzieren,aber auch den Abstand zwischen verschiedenen ICs und verbessern die Rechengeschwindigkeit des Chips. Was die Herstellungsmethode betrifft, es ist anders zu setzen ICs zusammen in der IC Entwurfsphase, und dann eine Maske durch den zuvor beschriebenen Designprozess erstellen.

Ein SOC hat jedoch nicht nur Vorteile, sondern die Entwicklung eines SOC erfordert auch eine erhebliche technische Zusammenarbeit. Wenn IC-Chips verpackt werden, sind sie durch ein externes Gehäuse geschützt, und der Abstand zwischen IC und IC ist groß, so dass es keine gegenseitige Beeinflussung gibt; wenn jedoch alle ICs zusammen verpackt werden, ist das der Anfang des Albtraums. Die IC-Design-Fabrik sollte sich vom ursprünglichen einfachen Design-IC zu einem IC entwickeln, der verschiedene Funktionen versteht und integriert, was die Arbeitsbelastung der Ingenieure erhöht. Darüber hinaus wird es viele Situationen geben, wie z. B. das Hochfrequenzsignal des Kommunikationschips, der IC wird mehr Funktionen haben.

Darüber hinaus muss SOC auch die Genehmigung für geistiges Eigentum (IP) von anderen Herstellern einholen, um von anderen entworfene Komponenten in SOC einzubauen. Da für die Herstellung von SOC die Entwurfsdetails des gesamten IC erforderlich sind, um eine vollständige Maske zu erstellen, steigen auch die Entwurfskosten für SOC. Manch einer mag sich fragen, warum nicht selbst entwerfen? Nur Unternehmen mit viel Geld wie Apple können das Budget aufbringen, um Top-Ingenieure von bekannten Unternehmen einzustellen, die ein brandneues Design entwerfen. IC. Es ist billiger, mit anderen zusammenzuarbeiten und eine Genehmigung einzuholen, als einen eigenen IC zu entwickeln.

Kompromiss, SIP erscheint

Als Alternative ist SIP auf die Stufe der Chipintegration aufgesprungen. Im Gegensatz zu SOC kauft es verschiedene ICs und kapselt sie ein letztes Mal, wodurch der Schritt der IP-Autorisierung entfällt und die Entwicklungskosten erheblich gesenkt werden. Da es sich um unabhängige ICs handelt, ist außerdem der Grad der gegenseitigen Beeinflussung stark reduziert.

Apple Watch nutzt SIP-Technologie für die Verpackung

Die bekanntesten Produkte mit SIP-Technologie sind Apple Watch.Da der Innenraum der Uhr zu klein ist,es keine traditionelle Technologie annehmen kann und die Designkosten von SOC zu hoch sind, ist SIP die erste Wahl geworden. Mit SIP-Technologie kann es nicht nur die Lautstärke reduzieren,sondern auch den Abstand zwischen jedem IC verkürzen, was zu einem machbaren Kompromiss geworden ist. Die folgende Abbildung ist das Strukturdiagramm des Apple Watch Chip.Sie sehen,dass eine beträchtliche Anzahl von ICs darin enthalten sind.

Internes Konfigurationsschema des S1-Chips

Nachdem die Verpackung abgeschlossen ist, muss die Testphase eingeleitet werden. In dieser Phase wird geprüft, ob die IC-Verpackung normal funktioniert. Wenn dies der Fall ist, kann er an das Montagewerk geliefert werden, um die elektronischen Produkte herzustellen, die wir sehen. Bisher hat die Halbleiterindustrie die gesamte Produktionsaufgabe abgeschlossen.

Es ist ein Profi R.D und Hersteller von hochpräzisen Leiterplatten. Es kann 4-46 Schichten von Leiterplatten in Massenproduktion produzieren,Leiterplatten,Hochfrequenzplatten, High-Speed Boards,HDI Platinen,Leiterplatten, Hochfrequenz Hochgeschwindigkeitsplatten,IC Verpackung Trägerplatten,Halbleiterprüfplatinen,Mehrschichtige Leiterplatten,HDI Leiterplatten,Mischspannungs-Leiterplatten, Hochfrequenz-Leiterplatten,Weiche und harte Kombiplatten, etc.