Heutzutage, CMOS-Technologie ermöglicht es einem FPGA-Gerät, mehrere I zu haben/O-Schnittstellen. Zur gleichen Zeit, in den letzten Jahren, Niedriger Stromverbrauch hat begonnen, zum Mainstream-Konzept der Hochgeschwindigkeits-I zu werden/O-Schnittstellen. Der effektivste Weg, den Stromverbrauch zu reduzieren, ist die Verringerung der Spannung, und die Spannungsreduktion führt zu einer geringeren Rauschgrenze, die durch das I erlaubt wird/O Schnittstelle. Daher, it is very necessary for FPGA users to quantify the system-level synchronous switching noise (SSN) in the chip, Paket, und PCB-Umgebung.

Dieser Artikel stellt SSN systematisch vor und konzentriert sich auf SSN, verursacht durch FPGA Output Puffering. Diese Art von Rauschen wird im Allgemeinen Synchronous Switching Output Noise (SSO) genannt, das sich von SSN unterscheidet, das durch Eingangspufferung verursacht wird. Dieser Artikel stellt die Ursachen von SSO auf Systemebene vor und schlägt eine mehrschichtige SSO-Modellierungsmethode auf Systemebene vor. Gleichzeitig wird in diesem Artikel auch erläutert, wie man das SSO-Modell mit Frequenzbereichs- und Zeitbereichsmessungen assoziiert und mehrere PCB-Designmethoden zur Reduzierung von SSO enthält.

Der Entstehungsmechanismus der SSO auf Systemebene

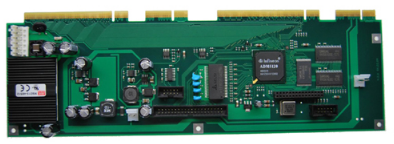

Eine Leiterplatte mit FPGA ist ein komplexes System, das in einen Chipteil unterteilt werden kann, der aktive Schaltungen enthält, Ein Gehäuseteil mit eingebetteten passiven Komponenten, die Leiterbahnen unterstützen, und ein Leiterplattenteil, das Verbindungen zwischen dem FPGA und der Außenseite bietet. In dieser Art von System, Es ist schwierig, die Geräuscheigenschaften im Inneren des Chips zu verstehen. Daher, Es ist sehr wertvoll, den SSO am nahen und fernen Ende der Leiterplatten-Spuren mit dem FPGA verbunden. There are two main factors that cause SSO: the impedance of the power distribution network (PDN) and the mutual inductance coupling between the switch I/O.

Aus Systemsicht umfasst PDN Komponenten auf Wafer-, Paket- und Platinenebene, die zusammen Strom für CMOS-Schaltungen liefern. Wenn eine bestimmte Anzahl von CMOS-Ausgangsantriebsschaltungen gleichzeitig eingeschaltet wird, fließt sofort ein großer Strom in die induktiven Schaltungselemente des PDN, was zu einem Delta-I-Spannungsabfall führt. Interconnect-Strukturen erzeugen parasitäre Induktivitäten, wie z.B. Power-Lötkugeln auf dem Kugelgitter-Array-Paket und Power-Vias in der Leiterplatte. Dieser schnell wechselnde Strom regt auch radiale elektromagnetische Wellen zwischen dem Leistungs-/Masseebenen-Paar an. Die elektromagnetischen Wellen werden von der planaren Kante der Leiterplatte reflektiert, wodurch Resonanz zwischen der Leistungs-/Masseebene entsteht und Spannungsschwankungen verursacht werden.

Eine weitere wichtige Ursache für SSO ist die gegenseitige Induktivitätskopplung, insbesondere die gegenseitige Induktivitätskopplung um das Chippaket/Leiterplattenkante. Die Lötkugeln auf dem Chip-BGA-Paket und die Vias auf der Leiterplatte gehören zu einer dicht gekoppelten Mehrdrahtstruktur. Jede I/O-Lötkugel und ihre entsprechende Leiterplatte über und ihre nächstgelegene Erdlötkugel und Erdung über bilden eine geschlossene Schleife. Wenn sich der Zustand mehrerer I/O-Ports gleichzeitig ändert, fließen transiente I/O-Ströme durch diese Signalschleifen. Dieser transiente I/O-Strom erzeugt ein zeitvariierendes Magnetfeld, das in benachbarte Signalschleifen eindringt und induziertes Spannungsrauschen verursacht.

Ein ausgezeichnetes SSO-Modell sollte in der Lage sein, den grundlegenden Formationsmechanismus von SSO widerzuspiegeln. Ein geschichtetes Modell zur Vorhersage von SSO in Leiterplatten. Auf Chipebene, Was wir brauchen, ist ein Ausgangspuffermodell, das eine genaue Stromverteilung auf Stromleitungen und Signalleitungen mit begrenzter Komplexität bereitstellen kann. Auf Verpackungsebene, für Einfachheit, Modellierungswerkzeuge können verwendet werden, um das PDN-Modell und das Signalkopplungsmodell zu erhalten, Die Interaktion zwischen dem PDN und dem Signalkopplungsmodell sollte jedoch sorgfältig geprüft werden. Diese beiden Modelle fungieren als Brücke, Anschluss des Ausgangspuffermodells am Bump-Ende des Chippakets und des PCB-Level-Modells am Lötkugel-Ende. Das PDN-Modell der Leiterplatte beinhaltet normalerweise die Leistung/Bodenfläche und die große Kapazität/Entkopplung der Kondensatoren, während das Signalkopplungsmodell der PCB beinhaltet Eine fest gekoppelte über Array und lose gekoppelte Signalspuren auf verschiedenen Signalschichten. Der Wechselwirkungseffekt dieser beiden PCB-Level-Modelle erscheint in der PCB über Array. Von hier aus bringt induktives Übersprechen Rauschen in das PDN-Modell, Das Delta-I-Rauschen wiederum reduziert die Qualität des I/O-Signal. Diese hierarchische Modellierungsmethode hält die Simulationsgenauigkeit angemessen aufrecht, und gleichzeitig die Recheneffizienz solcher komplexen Systeme verbessert.