現今, CMOS科技允許FPGA器件具有多個I/O介面. 同時, 近年來, 低功耗已開始成為高速I的主流概念/O介面. 降低功耗的最有效方法是降低電壓, 電壓降低將導致I允許的較小雜訊容限/O介面. 因此, it is very necessary for FPGA users to quantify the system-level synchronous switching noise (SSN) in the chip, 包裹, 和 PCB環境.

本文系統地介紹了SSN,重點介紹了FPGA輸出緩衝引起的SSN。 這種雜訊通常稱為同步開關輸出雜訊(SSO),與輸入緩衝引起的SSN不同。 介紹了系統級單點登錄產生的原因,提出了一種分層的系統級單點登錄建模方法。 同時,本文還解釋了如何將單點登錄模型與頻域和時域量測相關聯,並給出了幾種减少單點登錄的PCB設計方法。

系統級單點登錄的形成機制

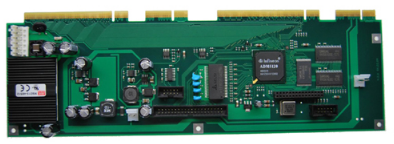

帶有FPGA的PCB是一個複雜的系統,可以分為包含有源電路的晶片部分, 帶有支持軌跡的嵌入式無源元件的封裝部件, 以及電路板部分,其提供FPGA和外部之間的連接. 在這種類型的系統中, 很難理解晶片內部的雜訊特性. 因此, 在系統的近端和遠端量化SSO是非常有價值的 PCB軌跡 連接到FPGA. There are two main factors that cause SSO: the impedance of the power distribution network (PDN) and the mutual inductance coupling between the switch I/O.

從系統角度來看,PDN包括晶圓級、封裝級和板級組件,它們共同為CMOS電路提供電源。 當一定數量的CMOS輸出驅動電路同時接通時,大電流將瞬間流入PDN的感應電路元件,導致delta-I電壓降。 互連結構產生寄生電感,例如球栅陣列封裝上的功率焊球和PCB中的功率過孔。 這種快速變化的電流也會在電源/接地層對之間激發徑向電磁波。 電磁波從PCB的平面邊緣反射,在電源/接地層之間產生共振,並引起電壓波動。

SSO的另一個重要原因是互感耦合,尤其是晶片封裝/PCB邊緣周圍的互感耦合。 晶片BGA封裝上的錫球和PCB上的通孔屬於緊密耦合的多線結構。 每個輸入/輸出焊球及其對應的PCB通孔及其最近的接地焊球和接地通孔形成一個閉環。 當多個輸入/輸出埠的狀態同時改變時,瞬態輸入/輸出電流流過這些訊號回路。 這種瞬態輸入/輸出電流將產生時變磁場,侵入相鄰的訊號環路並引起感應電壓雜訊。

一個優秀的單點登錄模型應該能够反映單點登錄的基本形成機制. 預測印刷電路板單點登錄的分層模型. 在晶片級, 我們需要的是一個輸出緩衝模型,該模型可以以有限的複雜性在電力線和訊號線上提供精確的電流分佈. 在包裝層面, 為了簡單起見, 建模工具可用於獲得PDN模型和訊號耦合模型, 但是,應仔細考慮PDN和訊號耦合模型之間的相互作用. 這兩個模型起到了橋樑的作用, 連接晶片封裝凸塊端的輸出緩衝模型和焊球端的PCB級模型. PCB的PDN模型通常包括電源/地平面和大容量/其上的去耦電容器, 而訊號耦合模型 PCB包括 緊密耦合的過孔陣列和不同訊號層上的鬆散耦合訊號軌跡. 這兩個PCB級模型的互動效應出現在PCB過孔陣列中. 正是從這裡,感應串擾將雜訊引入PDN模型, 而delta-I雜訊反過來會降低I的質量/O訊號. 這種分層建模方法合理地保持了模擬精度, 同時提高了此類複雜系統的計算效率.