(1) 전자 시스템 설계의 당면 과제

시스템 설계의 복잡성과 집적도가 대규모로 증가함에 따라 전자 시스템 설계자는 100MHZ 이상의 회로 설계에 종사하고 있으며, 버스의 작업 주파수는 이미 50MHZ에 도달했거나 초과하였고, 일부는 심지어 100MHZ를 초과하였다.현재 약 50% 의 시계 주파수가 50MHz를 초과하고 거의 20% 의 시계 주파수가 120MHz를 초과하도록 설계되었습니다.

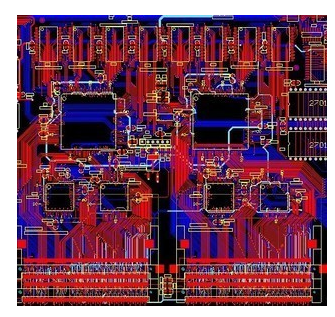

시스템이 50MHz에서 작동하면 전송선 효과와 신호 무결성 문제가 발생합니다.시스템 클럭이 120MHz에 도달하면 고속 회로 설계 지식을 사용하지 않는 한 기존 방법을 기반으로 설계된 PCB가 작동하지 않습니다.따라서 고속 PCB 설계 기술은 전자 시스템 설계자가 반드시 채택해야 할 설계 방법이 되었다.설계 과정의 통제성은 고속 회로 설계자의 설계 기술을 사용해서만 실현할 수 있다.

(2) 고속 회로란 무엇인가

일반적으로 디지털 논리 회로의 주파수가 45MHZ~50MHZ에 도달하거나 초과하고 그 주파수 이상에서 작동하는 회로가 이미 전체 전자 시스템의 일정 부분 (예: 1/3) 을 차지한다면 고속 회로라고 한다.

사실 신호 가장자리의 고조파 주파수는 신호 자체의 주파수보다 높다.신호의 상승 및 하강 (또는 신호 홉) 은 신호 전송에 예기치 않은 결과를 초래할 수 있습니다.따라서 회선 전파 지연이 디지털 신호 구동단의 상승 시간의 1/2보다 크면 이 신호는 고속 신호로 간주되고 전송 회선 효과가 발생한다는 것이 일반적인 견해이다.

신호의 전송은 상승 또는 하강 시간과 같이 신호 상태가 변하는 순간에 발생합니다.신호는 구동단에서 수신단까지 일정한 시간을 거친다.전송 시간이 상승 또는 하강 시간의 1/2보다 작으면 수신 측의 반사 신호가 신호가 변경되기 전에 구동 측에 도달합니다.반대로 신호가 상태를 바꾸면 반사 신호가 구동단에 도달한다.반사 신호가 강하면 중첩된 파형이 논리 상태를 변경할 수 있습니다.

(3) 고속 신호의 확정

위에서 우리는 이미 전송선 효과가 발생하는 선결 조건을 정의했지만, 우리는 어떻게 회선 지연이 구동단 신호 상승 시간의 1/2보다 큰지 알 수 있습니까?일반적으로 신호 상승 시간의 일반적인 값은 장치 매뉴얼에서 제공 될 수 있으며 신호 전파 시간은 PCB 설계의 실제 경로설정 길이에 따라 결정됩니다.신호 상승 시간과 경로설정 허용 길이 (지연) 간의 상관 관계.

PCB의 인치당 지연은 0.167ns입니다. 그러나 네트워크 케이블에 많은 오버홀, 많은 장치 핀, 많은 구속이 설정되어 있으면 지연이 증가합니다.일반적으로 고속 로직 부품의 신호 상승 시간은 약 0.2ns다. 보드에 GaAs 칩이 있으면 최대 케이블 길이는 7.62mm다.

Tr을 신호 상승 시간으로 설정하고 Tpd를 신호선 전파 지연으로 설정합니다.Tr☎ 4Tpd이면 신호가 안전합니다.2Tpd–$Tr–$4Tpd이면 신호가 불확실성 영역으로 떨어집니다.Tr–2Tpd이면 신호가 문제 영역에 속합니다.불확실한 영역과 문제 영역에 떨어진 신호의 경우 고속 PCB 경로설정 방법을 사용해야 합니다.