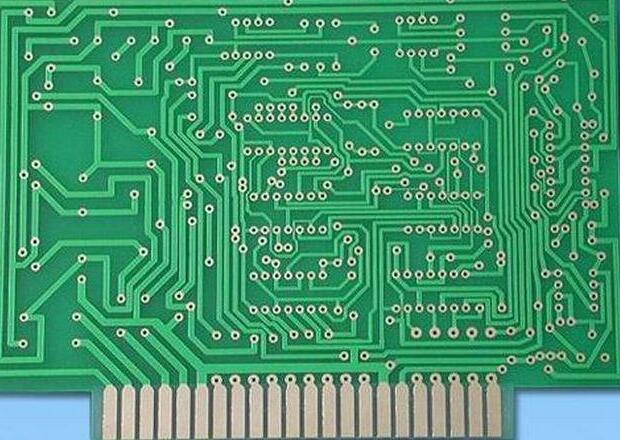

PCB 설계에서 파이톤 등거리 설계가 필요한 이유

PCB 설계에서 등장적선은 주로 일부 고속병렬버스에 사용된다.이 유형의 병렬 버스는 일반적으로 동일한 클럭 샘플링에 기반한 여러 데이터 신호를 가지기 때문에 각 클럭 주기마다 두 번(DDRSDRAM) 또는 네 번 샘플링이 필요할 수 있습니다.칩의 작업 주파수가 증가함에 따라 신호 전송 지연이 시퀀스에 미치는 영향은 갈수록 커진다.모든 신호의 값이 데이터 샘플링 포인트 (시계의 상승 또는 하강 연) 에서 올바르게 수집되도록 하려면 신호 전송 지연을 제어해야 합니다.등장적선은 PCB에 있는 모든 관련 신호의 전송 지연 차이를 최소화하기 위한 것이다.고속 신호의 효과적인 설정과 유지 관리 창은 상대적으로 작다.데이터와 제어 신호를 유효한 창에 떨어뜨리기 위해 데이터, 시계 또는 데이터 간, 그리고 제어 신호 간의 흔적선 길이의 차이는 매우 작다.구체적인 허용 편차는 시간 지연을 계산하여 얻을 수 있다.

사실상 일반적으로 시차론리신호는 반드시 설정시간과 유지시간을 만족시켜야 하며 일정한 여유를 가져야 한다.이 조건만 충족하면 신호의 길이가 엄격하게 같지 않을 수도 있다. 그러나 실제 상황은 고속 신호(예: DDR2, DDR3, FSB)의 경우 설계 과정에서 시퀀스가 설정 시간과 유지 시간 요구를 충족하는지 알 수 없다(칩의 내부 배선과 용량을 포함한 영향 요소가 너무 많다).부하로 인한 지연 차이를 고려해야 하며 계산을 통해 실제 값을 추정하기 어렵습니다.) 칩 내부에 제어 가능한 지연 장치 (지연은 레지스터에 의해 제어됩니다.) 를 설정하고 레지스터의 값을 스캔하여 다양한 지연을 시도해야 합니다.또한 신호를 관찰하여 (파형을 직접 관찰하고 설정 및 유지 시간을 측정) 지연 값을 결정하여 설정 시간 및 유지 시간 요구 사항을 충족시킵니다.그러나 일반적으로 하나 이상의 신호선에서만 동일한 유형의 신호가 관찰됩니다.모든 신호가 타이밍 요구 사항에 부합하도록 동일한 유형의 신호 배선은 길이에서 엄격하게 동일해야 합니다. 우리는 대리상이 아닙니다. 우리 공장은 중국에 있습니다.수십 년 동안 선전은 세계 전자 연구 개발 및 제조 센터로 알려져 왔습니다.우리의 공장과 사이트는 모두 중국 정부의 비준을 받았기 때문에 당신은 중개상을 건너뛰고 안심하고 우리의 사이트에서 제품을 구매할 수 있습니다.우리는 직영 공장이기 때문에, 이것은 우리의 100% 오래된 고객이 iPCB에서 계속 구매하는 이유입니다.최소 요구 사항은 없습니다.당신은 우리에게서 1 위안의 PCB를 주문할 수 있습니다.우리는 당신이 정말로 필요하지 않은 것을 구입하여 돈을 절약하도록 강요하지 않습니다.무료 DFM은 당신이 가장 적시에 지불하기 전에,숙련된 전문 기술자가 모든 주문에 대한 무료 엔지니어링 서류 검토 서비스를 제공합니다.