回路 基板の設計は、非常に時間がかかり、時間がかかります。どんな問題でも、エンジニアはコンポーネントによってコンポーネントの全体のデザインをチェックする必要があります。回路基板の設計要件はチップ設計と同じであると言える。

典型的な PCB設計 プロセスには次の手順が含まれます。

最初の3つのステップは、概略チェックが手動処理であるので、最も時間がかかります。1000以上の接続を持つSoCボードを想像してください。手動で各接続をチェックする退屈な作業です。事実上、すべての接続をチェックするのはほとんど不可能です。そして、それは不正確な接続、浮動ノードなどの最終的な板の問題を引き起こすかもしれません。

回路図キャプチャステージは通常、以下のような問題に直面します。

アンダースコアエラー:例えば、APLLVDDと

ケース質問:VDDEとVDDEのような

スペルミス

信号短絡問題

ほかにも

これらのエラーを避けるために、数秒以内に完全な回路図をチェックする方法があるはずです。この方法は,回路基板設計プロセスにおいては珍しい回路図シミュレーションで実現できる。回路図シミュレーションを使用すると、希望するノード上の最終的な出力を表示することができますので、自動的にすべての接続の問題をチェックします。

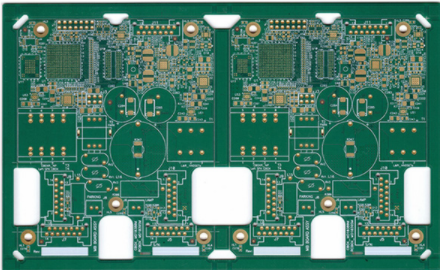

以下にプロジェクト例を挙げて説明する。典型的な回路基板ブロック図を考える

ハウツーとスタイル PCB設計 エラーと改善のデザイン効率 PCBレイアウト

複雑な回路基板設計では、何千ものデジタル接続があり、いくつかの変更は、検査のために多くの時間を無駄にすることがある。

概略シミュレーションは、設計時間を節約するだけでなく、回路基板の品質を向上させ、全体的なプロセス効率を向上させることができる。

典型的なDUTには以下のシグナルがあります。

いくつかの事前調整の後、試験中のデバイスは、電圧調整器、演算増幅器などのような信号調整のための様々な信号および様々なモジュールを有する。電圧調整器によって得られる電力信号の一例を考える

接続を確認し,全体的な検査を行うため,概略シミュレーションを使用した。概略シミュレーションは、概略作成、テストプラットフォームの作成およびシミュレーションを含みます。

テストプラットホームの作成の間、刺激シグナルは必要な入力に送り出される。そして、出力は利息のシグナルポイントで観測される。

以上の処理は、プローブを観察するノードに接続することで実現できる。ノード電圧および波形は、回路図にエラーがあるかどうかを示すことができる。すべての信号接続が自動的にチェックされます。

ハウツーとスタイル PCBメーカー エラーを減らす PCB設計 そしてそれらの設計効率を改善する

見てみましょう、検出されたノードと電圧ははっきりと見えます。

シミュレーションの助けを借りて直接結果を観測し,PCBボードの回路図が正しいことを確認できた。さらに,刺激信号や成分値を慎重に調整することで,設計変更を検討することができる。このため,回路シミュレーションや検査員の多くの時間を節約でき,設計の正当性を高めることができる。