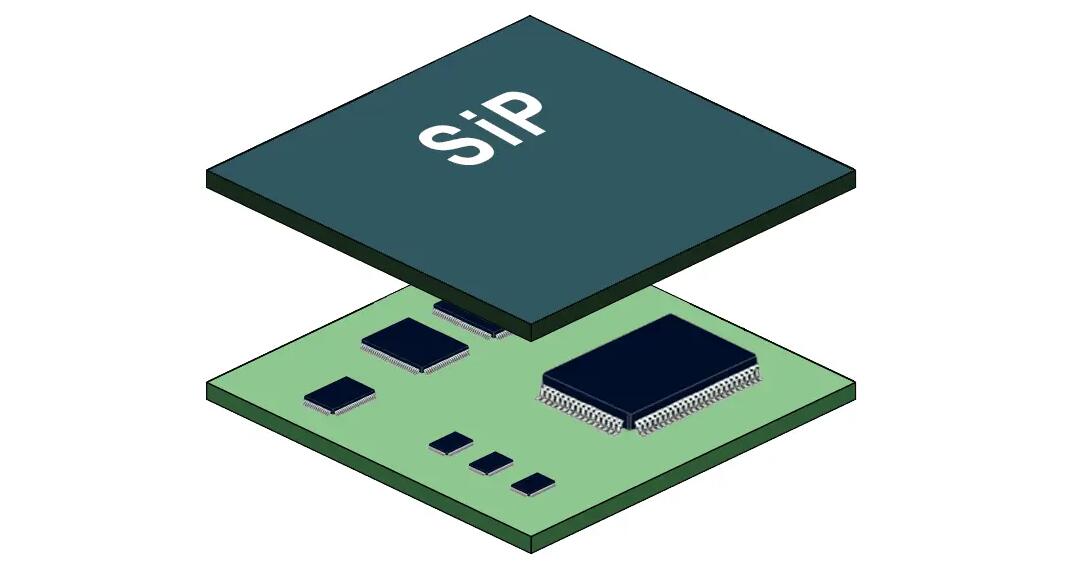

システムレベルパッケージ(SIP)は、PoP、CoC、WLP、TSV、埋め込み基板などを含む簡単なパッケージ技術ではありません。リードボンディング、フリップチップ、マイクロバンプなどの他のパッケージ技術の開発にも関連しています。

スタック包装(PoP)

スタックパッケージ(PoP)は、より小さなスペースでより多くの機能を提供することができます。スタックパッケージは、異なる機能を持つマルチチップパッケージを開発したり、容量が増加したパッケージに複数のメモリチップを配置したりするために使用できます。システムレベルパッケージ(SiP)は、単一パッケージにおいて様々なシステムコンポーネントを実装することができる。これらの技術により、半導体会社は高付加価値の製品を創造することができ、同時に市場の多様な需要を満たすことができる。

包装スタックは、垂直スタック包装のプロセスである。パケット対パケットスタック(PoP)は最も一般的なスタック方法であり、モバイルデバイスで広く応用されている。モバイルデバイスのPoPでは、上下のパッケージに使用されるチップのタイプや機能が異なる場合があり、チップメーカーが異なる場合があります。

一般的なPoPでは、上のパッケージには主に半導体ストレージ社製のメモリチップが含まれていますが、下のスタックパッケージには主にモバイルプロセッサ付きのチップが含まれています。包装は異なるメーカーが生産しているため、積む前に品質検査を行う必要があります。積層後に欠陥が発生しても、欠陥のあるコンポーネントを新しいパッケージに置き換えて再加工することができます。

チップオンチップ(CoC)

COCパッケージ技術は一般的な集積回路パッケージ技術であり、電子製品製造分野に広く応用されている。COC(チップオンチップ)は複数のチップを同一パッケージにパッケージ化する技術である。複数のチップを積層することで、回路の集積度を効果的に高め、回路基板のサイズを小さくし、回路の性能と信頼性を高めることができる。

COCパッケージのプロセスでは、最初のステップはチップの選択とテストです。チップ選択とは、チップの品質と性能を確保するために厳格なテストとスクリーニングが必要な大量のチップの中から、要求に合ったチップを選択することを意味します。次に、正確な位置決めとスタック技術を使用して複数のチップをスタックし、全体を形成します。スタック中には、チップの正確な位置決めを確保し、パッケージ中に安定性を維持するために、正確な位置決め装置と接着剤が必要です。

COCパッケージ技術の鍵はチップの接続にある。スタック後、チップを電気的に接続して、データの転送と通信を実現する必要があります。これは通常、マイクロ溶接またはケーブル接続によって実現されます。マイクロ溶接は、チップ間を接続するために微小な溶接点を使用するピンであり、ケーブル接続は、チップ間を接続するために小さなワイヤを使用するピンである。これらの接続には、信頼性と安定性を確保するための正確な操作と高度な技術的要件が必要です。

包装が完了したら、外観処理とテストを行う必要があります。外観処理とは、製品の外観と品質を向上させるために包装体を美化し、保護することを意味する。このプロセスには、包装体のコーティング、研磨、研磨、ラベルと包装の完成が含まれます。テストとは、パッケージチップの電気的性能と信頼性のテストを行い、設計要件に適合し、正常に動作することを保証することです。

COC包装技術の応用は非常に広い。マイクロプロセッサ、メモリ、通信チップなど、さまざまな集積回路をカプセル化するために使用できます。COC包装技術は回路の集積度と性能を高め、回路基板のサイズを減らし、システムの消費電力を下げ、システムの信頼性と安定性を強化することができる。そのため、携帯電話、タブレット、テレビ、カメラなどの電子製品の製造に広く応用されている。

COCパッケージ技術は、複数のチップを同一パッケージにパッケージ化する技術である。チップの選択、スタック、接続、外観処理、テストなどのプロセスを通じて、回路集積、小型化、高性能を実現しました。COCパッケージプロセスは電子製品の製造において重要な役割を果たしている。それは回路の性能と信頼性を高めるだけでなく、製品のサイズと消費電力を下げるためである。

システムレベルパッケージング(SIP)

システムレベルパッケージ(SIP)の利点

1.パッケージ効率が高く、SiPパッケージ技術は同一パッケージ内に複数のチップを追加し、パッケージ体積を大幅に減少させ、パッケージ効率を向上させた。

2.製品の発表周期が短く、SIPパッケージはSOCと異なるため、レイアウトレベルでレイアウトと配線を行う必要がなく、設計、検証とデバッグの複雑性を下げ、システムの実現時間を短縮した。一部の設計変更が必要でも、Socよりずっと簡単です。

3.互換性が良く、SIPパッケージは異なるプロセスと材料で作られたチップを1つのシステムに組み合わせ、埋め込み型集積受動素子の夢の組み合わせを実現することができる。現在、無線および携帯型電子機器に使用されている受動素子は、少なくとも30〜50%のμmを埋め込むことができる。

4.システムコストを削減し、SIPは低消費電力と低ノイズのシステムレベル接続を提供することができ、より高い周波数で動作することで、より広い帯域幅とほぼSOCと同じバス帯域幅を実現することができる。SIPパッケージ技術を用いた専用集積回路システムは、SOCよりも多くのシステム設計と生産コストを節約することができる。

5.物理サイズが小さく、SIPパッケージの厚さが絶えず減少している。最先端の技術では、5層積層チップの厚さがわずか1.0 mmの超薄型パッケージを実現し、3層チップパッケージの重量を35%軽減することができます。

6.電気性能が高く、SIPパッケージ技術は複数のパッケージを1つに組み合わせることができ、溶接点の総数を大幅に減少させ、パッケージの体積と重量を著しく低下させ、素子の接続経路を短縮し、それによって電気性能を向上させる。

7.応用が広く、SIPパッケージは従来のチップパッケージとは異なる。デジタルシステムだけでなく、光通信、センサ、マイクロ電気機械システム(MEMS)などの分野にも応用できる。

SIPパッケージの主な応用分野

SIPは無線通信、自動車電子、医療電子、コンピュータ、軍事電子などの広範な応用を持っている。その中で最も広く応用されている分野は無線通信である。

SIPは無線通信分野で最も古く、広く使用されている。無線通信の分野では、機能の伝送効率、ノイズ、体積、重量、コストに対する要求が高まっており、無線通信を低コスト、携帯、多機能、高性能の方向に発展させている。

SIPは理想的なソリューションであり、既存のコア資源と半導体生産プロセスの利点を結合し、コストを削減し、発売時間を短縮し、SOCにおけるプロセス互換性、信号混合、ノイズ干渉、電磁干渉などの困難を克服した。

SIPパッケージ技術は先進的なシステム統合とパッケージ技術である。他のパッケージ技術と比べて、SIP技術は一連の独特な技術優勢を持っており、現在の電子製品のより軽く、より小さく、より薄い発展需要を満たしている。それはマイクロエレクトロニクスの分野で広い応用市場と発展の見通しを持っている。