T何 全体 プロセス 分析 of <エー href="エー_href_0" tエーrゲット="_bl安k">PCB設計 缶 ビー 大ざっぱ 分かれた インto the followインg ステージ ネットリスト 輸入, パッケージ 図書館 ビル, メイン デザイン, 物理 安d 電気 制約 デザイン, レイアウト, 配線, デザイン レビュー, エーnd デザイン 出力. For エー 複合体 デザイン, から the 見通し of the タスク 自体, レイアウト 安d 配線 エーre 比較的 the 大部分 親しい, 特に 配線. から the 長期 実際 経験, マニュアル 配線 of 重要 シグナル is 静止 the メイン フォーム of 配線.

考慮 the 複雑さ 安d 大胆さ of the 配置 and ルーティング タスク プロセス, a 並列 デザイン 方法 is 考慮. 並列 PCB デザイン 方法 for レイアウト and ルーティング are bエーSically 類似, でも the 目的 and フォーカス are 異なる. The followインg takes レイアウト エーS an 例, and a ブリーフ 説明 意志 ビー メイド on the スペシャル ポイント of 並列 配線 デザイン.

タスク解析と分解

レイアウト解析の出発点は構造設計制約と回路トポロジー解析である。構造設計の制約は、フレームの形状とサイズ要件、取付穴と特別なコンポーネントの位置決めと高さの制限要件、および地域の使用の制約が含まれます。

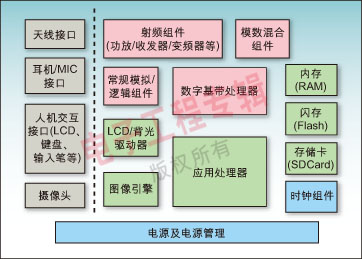

典型的な設計例を考えてください。そして、例として携帯電話ボード設計をします。回路トポロジーから観察すると、一般的な原理ブロック図を図1に示す。図1を見ると、各部品の信号特性はレイアウト要件に明らかな違いがあることが分かる。信号の流れに応じて各コンポーネントのレイアウトを拡張し,シールドや電磁両立性(emc)などの設計要件を考慮する。製品信頼性と安定性については,信号完全性(si)問題も考慮しなければならない。

以上のような代表的な設計例を解析した後、回路トポロジー型による展開、各構成要素に適した空間を計画し、並列設計レイアウトに適した技術者を配置する並列設計レイアウト方法を得ることができた。

役割配置

図1を例として、以下の並列設計レイアウトのタスク分解を考察する

(1)無線周波数成分(パワーアンプ/トランシーバ/インバータ等)、アナログデジタルハイブリッド部品、従来のアナログ/論理部品、デジタルベースバンドプロセッサ等を含む通信プロトコル関連グループ;

(2)液晶/バックライトドライバ、画像処理エンジン、アプリケーションプロセッサ、メモリ(( RエーM ))、フラッシュメモリ(フラッシュメモリ)、ストレージ(SDカード)等を含むアプリケーション関連のグループ

(3)周辺インターフェース、電源及び電力管理、時計部品等を含む共通信号関連グループ。

It is エーSsumed あれ それぞれ of the 並列 phエーSes is エーSsumed and 完成 そば an エンジンer. Then there are the followインg 役割 代入 エンジニア A is 責任 for レイアウト デザイン and コミュニケーション プロトコル グループ レイアウト; エンジニア B is 責任 for アプリケーション-関連 グループ レイアウト; エンジニア C is 責任 for public シグナル-関連 グループ レイアウト. The 原理 of 役割 アレンジment is to フォーカス on the スキル and 専門知識 of それぞれ エンジニア.

レイアウト 並行 デザイン

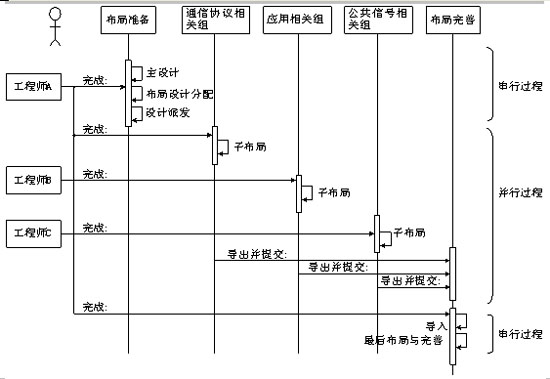

並列設計のシーケンス図である。その中で、エンジニアAは、メインデザイン(ネットリストのエントリをガイドし、構造制約設計を実行し、インストールホールを位置決めする段階的設計ドキュメント)を準備し、上述の分解方法に従ってサブレイアウト材料ラベルを計画し、設計要件に従ってレイアウト間隔を割り当て、タスク配布説明文書を作成する技術者は、電源原理設計図、材料費、タスク配布記述文書、PCBマスター設計ファイル等を他の2エンジニアに分割する。

各エンジニア(エンジニアAを含む)は、それぞれのレイアウト領域および関連する要件に従ってレイアウトを実行する。レイアウトが完了した後、それらのタスクに関連しないデバイスが削除されます。PCBツールソフトウェアを介してそれぞれのサブレイアウトファイルをエクスポートし、責任のあるエンジニアに提出します。

エンジニアAは、各サブレイアウトファイルを受信した後、彼はまだPCBのツールソフトウェアを介して順番に自分のサブレイアウトファイルにサブレイアウトファイルをインポートします。エンジニアAは、設計要件に従って最終的なレイアウト調整と最適化を行います。

配線の並列設計

配線解析の出発点は一般に回路トポロジーの電気信号の解析である。電気信号は2つのタイプに分けられることができます:重要なシグナル(厳しい電気的な制約をもつ信号)と非重要な信号。

上記の携帯電話機の設計例を考慮して、各部品の配線要件には明らかな相違がある。様々な電気的性能設計要件を考慮しながら、各構成要素の配線は、レイアウト要素および信号フローに従って、依然として拡張する必要がある。

上述の代表的な設計例では、回路トポロジー型(すなわち、必要領域分割)と信号フローを拡張して配線優先度を決定するようにした。高い優先度(多くの場合、多くの場合、多くの場合、配線)は、パフォーマンスと進歩を確実にするために優先順位を与えられます。

高い優先度の配線タスクに並列設計タスクを割り当てることを考え、最終的には責任あるエンジニアが最終的な改善と終了を行います。また、ツールの使用はレイアウト段階と異なります。エクスポートされ、インポートされたファイルは、配線ステージのサブデザインファイルです。

本稿要旨

携帯電話設計例の原理を解析した後,並列設計の方法について述べた。タスクの分割とツールの組合せによって,並列設計の操作が実現され,それは資源の相補的利点を達成するだけでなく,設計品質と時間スケジュール要求をも保証する。

The 上記 is the インtroduction to 並列 デザイン of 回路 板s.