Man mano che i progetti di circuiti stampati diventano più complessi, iniziano a spingere le prestazioni delle architetture hardware/power management esistenti ai loro limiti. Attualmente ci sono quattro architetture di gestione dei circuiti stampati più comunemente utilizzate. Sebbene tutti possano essere utilizzati per supportare questi progetti complessi, hanno più o meno bisogno di fare concessioni o compromessi in termini di scalabilità del progetto, carico di lavoro o costo.

Recentemente, è apparso il quinto tipo di architettura di gestione del circuito stampato, che può fornire le massime prestazioni, sicurezza e flessibilità attualmente, riducendo notevolmente il carico di lavoro di progettazione e i costi di costruzione. Questo articolo discuterà questa nuova architettura, concentrandosi sulle funzioni di gestione dell'energia che fornisce.

Panoramica

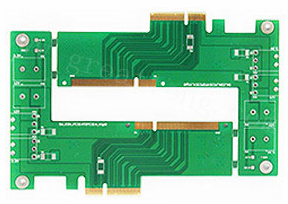

Di solito dividiamo un circuito stampato in due moduli funzionali (Figura 1) - gestione del carico (Gestione del carico utile) e gestione hardware (Gestione hardware). Per la maggior parte dei circuiti stampati, la funzione di carico rappresenta dall'80% al 90% dell'intera area PCB (strato dati/controllo e/o processore). Il restante 10-20% è la parte di gestione hardware, che viene utilizzata per eseguire il monitoraggio/controllo a livello hardware o la pulizia.

Fino a poco tempo fa è emersa una nuovissima architettura decentralizzata, più scalabile di altre architetture e può essere implementata a un costo BOM inferiore. Al fine di facilitare la comprensione dei vantaggi dell'architettura distribuita, discutiamo prima come costruire la funzione di gestione dell'energia delle quattro architetture di gestione hardware più comunemente utilizzate (Figura 2-5), e poi esploriamo ulteriormente l'architettura distribuita.

Confronto dell'architettura di gestione dell'energia basata su PLD di controllo

Gestione e pulizia dell'energia basate su CPLD, in questa architettura, le funzioni di gestione dell'energia vengono aggiunte al controllo PLD (CPLD) integrato. Il CPLD monitora la potenza in ingresso e il segnale "Power Good" di ogni convertitore DC-DC. Utilizzare CPLD per implementare l'algoritmo di temporizzazione per generare il segnale "Enable" per alimentare il circuito di carico per evitare danni o errori logici. Il CPLD può anche generare segnali logici, come i segnali Reset e Power Good, per garantire che i componenti del carico possano iniziare a funzionare quando l'alimentazione è accesa o si arrestano quando l'alimentazione è spenta. È inoltre responsabile della generazione di sequenze per disattivare in modo sicuro l'alimentazione in caso di interruzione di corrente o rilevamento di un guasto. PLD è facile da supportare soluzioni orientate agli eventi e può fornire risposte separate per diverse combinazioni di guasti.

Il sistema di gestione hardware basato su CPLD può realizzare funzioni di gestione dell'energia e pulizia

Per questo tipo di progettazione, tutte le funzioni di sequenza di potenza, protezione e controllo sono implementate utilizzando CPLD, di solito scritto in VHDL o Verilog.

vantaggio:

# Low cost #

L'architettura intuitiva rende la logica di temporizzazione del CPLD facile da adattare alle nuove applicazioni

â Utilizzare un ambiente di progettazione (comunemente usato Verilog) per realizzare il design

L'architettura orientata agli eventi può rispondere diversamente a vari fallimenti in modo flessibile

carenze:

Poiché ogni alimentatore richiede 2 canali di segnale, i progetti più grandi e complessi iniziano ad affrontare la sfida di più porte I/O CPLD e congestione dei circuiti stampati

Il buon rilevamento non è accurato (solitamente 8% al 20% tasso di errore) e la tendenza di non essere in grado di monitorare la tensione di alimentazione, con conseguente affidabilità ridotta

â Aggiunta della funzione di misurazione automatica (monitoraggio della tensione effettiva di alimentazione, non il segnale Power Good), deve essere aggiunto un convertitore A / D, che aumenta il costo e la complessità del circuito stampato

Un ingegnere a livello di scheda (con esperienza nel circuito digitale) è richiesto per costruire le funzioni richieste. In molti casi, questo tipo di ingegnere non è un esperto di alimentazione elettrica

Utilizzare IC di gestione dell'energia per impostare la gestione dell'energia e utilizzare CPLD per la pulizia

In questa architettura funzionalmente divisa, un IC di gestione dell'alimentazione è responsabile del monitoraggio e del sequenziamento del convertitore DC-DC del circuito stampato. Poiché l'IC di gestione dell'alimentazione può monitorare direttamente la tensione dell'alimentazione elettrica, può anche eseguire funzioni di messa a punto e margining. Il CPLD utilizza lo stato Power Good dell'alimentazione elettrica per generare i segnali necessari di controllo, stato e pulizia.

Questi progetti utilizzano spesso strumenti di configurazione basati su GUI per definire le funzioni IC di gestione dell'alimentazione, mentre la logica CPLD è definita utilizzando VHDL o Verilog.

vantaggio:

* Ridurre il numero di CPLD I/O, perché la funzione Enable può essere eseguita dall'IC di gestione dell'energia

Lo spazio della scheda è più generoso, che può ottenere un layout più semplificato e meno strati di PCB

* Monitorando direttamente la tensione di alimentazione, l'IC di gestione dell'alimentazione può ottenere informazioni generali più accurate sulla salute del sistema e migliorare la stabilità del sistema

carenze:

â L'IC di gestione dell'energia aumenta il costo del BOM, specialmente quando sono necessari più componenti

â L'architettura può fornire una risposta orientata agli eventi, ma se più di due IC di gestione dell'energia sono implementati, aumenterà la complessità di progettazione

â La regolazione delle sequenze per progetti più complessi diventerà più difficile, specialmente quando si tratta di dividere le funzioni per più IC di gestione dell'energia

â Poiché il processo di progettazione deve utilizzare più strumenti (GUI + VHDL / Verilog), può richiedere più ingegneri, e aumenterà il rischio di progettazione

Utilizzare CPLD per implementare la pulizia e PMBus per implementare funzioni di gestione dell'energia basate su MCU. L'architettura utilizza un microcontrollore (MCU) per controllare la sequenza di potenza del punto di carico controllato digitalmente (DPOL). L'MCU utilizza il bus di gestione dell'alimentazione (PMBus) per gestire DPOL-PMBus è un protocollo di comunicazione a due fili basato sul bus I2C. Il CPLD è responsabile delle funzioni di pulizia a bordo e del controllo di qualsiasi convertitore DC-DC a punto di carico con un'interfaccia di controllo analogica (APOL). Al fine di semplificare la progettazione del software, la maggior parte dei progetti di gestione dell'energia basati su MCU adottano schemi di serie temporali.

C'è un altro potenziale svantaggio della gestione dell'alimentazione basata su software, che è la necessità di tempi di risposta dei guasti più lunghi (solitamente da 10 a 15 millisecondi, mentre il tempo di risposta del CPLD è microsecondi). Per alcuni guasti che richiedono tempi di risposta più rapidi (o sequenza orientata agli eventi), CPLD può essere aggiunto come seconda misura di protezione.

La realizzazione della gestione dell'alimentazione basata su software richiede VHDL o Verilog per il software MCU e la progettazione CPLD.

vantaggio:

â Il design è molto facile da regolare (solo per le serie basate sul tempo)

Gli strumenti di sviluppo software abbondanti rendono le soluzioni basate su MCU più veloci e convenienti per il debug.

* Aggiornare il firmware per cambiare rapidamente il design

Semplifica la progettazione PCB-il cablaggio intorno DPOL è più in eccesso

carenze:

# Più costoso costo BOM #

È difficile regolare il design per i requisiti di sequenza orientati agli eventi

â richiede più strumenti di progettazione (Verilog / VHDL + software)

Riassuma

Con la crescente complessità progettuale dei sistemi a livello PCB, i sistemi di gestione hardware rappresentano una percentuale crescente sia del carico di lavoro di progettazione che dei costi BOM. L'utilizzo di alimentatori CPLD e POL per implementare alcune o tutte le funzioni di gestione può alleviare le difficoltà causate dalle tendenze sopra menzionate, ma in questo momento il costo è diventato un ostacolo. Ora è disponibile un'architettura di gestione hardware distribuita e i CPLD possono essere collegati a componenti di rilevamento a basso costo tramite un collegamento seriale a 3 fili. Oltre a ridurre la complessità di progettazione, i requisiti di spazio PCB e i costi BOM, l'architettura può anche essere costruita utilizzando una varietà di strumenti di ingegneri analogici e digitali.