由於開關電源的開關特性, 開關電源容易產生很大的電磁相容干擾. 作為供電工程師, 電磁相容性工程師, 或者 PCB板佈局 工程師, 您必須瞭解電磁相容性問題的原因並採取措施, 尤其是佈局工程師, 需要瞭解如何避免污點擴大, this article mainly introduces

The main points of the power supply PCB板 討論了設計.

2.9佈局和 PCB板

1 幾個基本原則:任何導線都有阻抗; 電流總是自動選擇阻抗的路徑; 輻射强度與電流有關, 頻率, 和環路面積; 共模干擾與大dv的互電容有關/dt訊號接地; 减少電磁干擾和增强抗干擾能力的原理類似.

2. 佈局應根據電源劃分, 類比, 高速數位和每個功能塊.

3 最小化大di的面積/dt loop and reduce the length (or area, 大dv的寬度/dt訊號 line). 跡線面積的新增將新增分佈電容. 一般方法是:軌跡的寬度儘量大, but remove the excess part), 試著走直線, 减少隱藏的封閉區域以减少輻射.

4 感應串擾主要是由較大的di引起的/dt loop (loop antenna), 感應强度與互感成正比, so it is more important to reduce the mutual inductance with these signals (the main way is to reduce the loop area and increase the distance); Sexual crosstalk is mainly generated by large dv/dt訊號, 感應强度與互電容成正比. All decrease the mutual capacitance with these signals (the main way is to reduce the effective coupling area and increase the distance. 互電容隨著距離的新增而减小. Faster) is more critical.

5 盡可能使用環路取消原則來路由, 並進一步减少大面積di/dt loops (similar to twisted pair, use the principle of loop cancellation to improve anti-interference ability and increase transmission distance).

6. 减少回路面積不僅可以减少輻射, 同時也降低了回路電感, 使電路效能更好.

7. 减少回路面積需要我們設計每條軌跡的返回路徑.

8. 什麼時候 倍數 PCB板 通過連接器連接, 還需要考慮使環路區域達到, 特別是對於大型di/dt訊號, 高頻訊號或敏感訊號. 訊號線對應於地線, 兩條導線盡可能靠近. 如有必要, twisted pair wires can be used to connect (the length of each twisted pair wire corresponds to an integer 倍數 of the noise half-wavelength). 如果你打開電腦主機殼, 您可以看到,從主機板到前面板的USB介面通過雙絞線連接. 可以看出,雙絞線連接對於抗干擾和减少輻射非常重要.

9. 對於數據電纜, 儘量在電纜中佈置更多地線, 並使這些地線均勻分佈在電纜中, 可以有效减少環路面積.

10. 儘管一些板間連接線是低頻訊號, because these low-frequency signals contain a lot of high-frequency noise (through conduction and radiation), 如果處理不當,很容易發出這些譟音.

11. 接線時, 首先考慮高電流痕迹和易受輻射的痕迹.

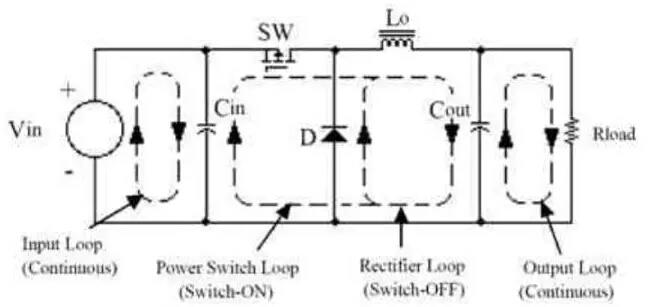

12. 開關電源通常有4個電流回路:輸入, 輸出, 轉換, 自由馳騁. 其中, 輸入和輸出電流回路幾乎是直流的, 幾乎不產生電磁干擾, 但他們很容易受到干擾; 開關和續流電流回路具有較大的di/dt, 這需要注意.

13. The gate drive circuit of the mos (igbt) tube usually also contains a large di/dt.

14. 不要放置小訊號電路, 例如控制和類比電路, 內部大電流, 避免干擾的高頻和高壓電路.

15. Reduce the susceptible (sensitive) signal loop area and trace length to reduce interference.

16. 小訊號軌跡遠離大dv/dt signal lines (such as the C pole or D pole of the switch tube, buffer (snubber) and clamp network) to reduce coupling, and ground (or power supply, 簡言之, often Potential signal) to further reduce the coupling, 地面應與地平面良好接觸. 同時, 小訊號記錄道應盡可能遠離大di/防止感應串擾的dt訊號線. 不要在大dv下跟踪小訊號/dt signal. If the back of the small signal traces can be grounded (the same ground), 還可以减少與之耦合的雜訊訊號.

17. 更好的方法是在這些大型dv周圍和背面鋪設地面/dt和di/dt訊號軌跡 (including the C/D poles of the switching devices and the switch tube heat sink), 並使用上層和下層進行接地. 連接通孔, and connect this ground to a common ground point (usually the E/開關管的S極, or sampling resistor) with a low-impedance trace. 這可以减少輻射EMI. 應注意,小訊號接地不得連接到此遮罩接地, 否則會產生更大的干擾. 大dv/dt軌跡通常通過互電容耦合干擾到散熱器和附近的地面. 將開關管散熱器連接至遮罩接地. 表面貼裝開關器件的使用也將减少互電容, 從而减少耦合.

18. 對於易受干擾的記錄道,不要使用過孔, 因為它會干擾過孔通過的所有層.

19. 遮罩可以减少輻射EMI, 但由於對地電容新增, conducted EMI (common mode, or extrinsic differential mode) will increase, 但只要遮罩層正確接地, 不會新增太多 . 可在實際設計中進行稱重和考慮.

20. 防止共阻抗干擾, 使用一點接地和一點供電.

21. 開關電源通常有3個接地:輸入電源大電流接地, 輸出功率大電流接地, 和小訊號控制接地. The ground connection method is shown in the following diagram:

22. 接地時, 首先應該判斷地面的性質, 然後進行連接. 採樣和誤差放大的接地通常應連接到輸出電容器的負極. 採樣訊號通常應從輸出電容器的正極選取. 共阻抗干擾. 通常,集成電路的控制接地和驅動接地不單獨引出. 此時, 採樣電阻器到地上的引線阻抗必須盡可能小,以减少共阻抗干擾並提高電流採樣的準確性.

23輸出電壓採樣網絡靠近誤差放大器,而不是輸出. 這是因為低阻抗訊號比高阻抗訊號更不容易受到干擾. 採樣軌跡應盡可能接近,以减少拾取的雜訊.

24. 注意電感的佈置要遠離並相互垂直,以减少互感, 尤其是儲能電感和濾波電感.

25. 當高頻電容器和低頻電容器並聯使用時,注意佈局, 高頻電容器離用戶很近.

26. Low-frequency interference is generally differential mode (below 1M), 高頻干擾通常為共模, 通常通過輻射耦合.

27. 如果高頻訊號耦合到輸入導線, it is easy to form EMI (common mode). 您可以在靠近電源的輸入導線上放置一個磁環. 如果電磁干擾降低, 這表明了這個問題. 該問題的解決方案是减少電路的耦合或EMI. 如果高頻雜訊未過濾乾淨並傳導至輸入導線, EMI (differential mode) will also be formed. 此時, 磁環不能解决這個問題. String two high-frequency inductors (symmetrical) where the input lead is close to the power supply. 下降表明存在此問題. 解决這個問題的方法是改進濾波, 或者通過緩衝减少高頻雜訊的產生, 夾緊和其他管道.

28. 差模和共模電流的量測.

29. EMI濾波器應盡可能靠近進線, 進線的佈線應盡可能短,以最小化EMI濾波器前後級之間的耦合. The incoming line is shielded with the chassis ground (the method is as described above). 輸出EMI濾波器應進行類似處理. 儘量新增進線和高dv之間的距離/dt signal traces, 應在 PCB板 layout.