現代電子設計において、PCB設計は極めて重要であり、バスは各種設備間通信の重要な通路として、PCB設計の性能と効率に基礎を提供した。本文は高速PCB設計における並列バスとシリアルバスの特徴、長所と短所及び応用シーンを深く検討し、設計エンジニアが適切なバスタイプをよりよく理解し選択するのを助ける。

バスは、2つ以上のデバイス間で通信する共有物理パス、信号線のセット、および複数のコンポーネント間で情報を送信するための共通リンクである。動作モードに応じて、バスには主にパラレルバスとシリアルバスの2種類があります。

並列バスは、マルチビットデータの同時転送を可能にするように設計されている。このバス構造は、同時に走行する複数の車両を収容できる広々とした道路に似ており、通常はデータ伝送要件が高い場合に使用されます。並列バスの利点は、複数の信号を同時に伝送できるため、データ伝送速度が速いことです。しかし、データ伝送速度の向上に伴い、信号の完全性と干渉の問題も発生した。並列バス接続にはより多くの信号線が必要であり、設計の複雑性が増加し、高周波動作において、信号間のクロストークと遅延の問題は無視できない。

パラレルバスとは異なり、シリアルバスはビット順に次々とデータを転送します。シリアル信号は通常、配線をより簡単に、より鮮明にするために、より少ない信号線を使用します。データ転送には1本または数本のワイヤしか必要としないため、シリアルバスはPCBに占有されるスペースを減らし、完成品の複雑さを減らす上で特に重要である。

シリアルバスは一般的に干渉に強く、特に差動信号を使用する場合、各差動線は正極と負極からなり、信号の完全性が向上します。シリアルバスの単位時間当たりの伝送ビット数は少ないが、より高い伝播速度を使用することでより高いデータレートを実現することができる。

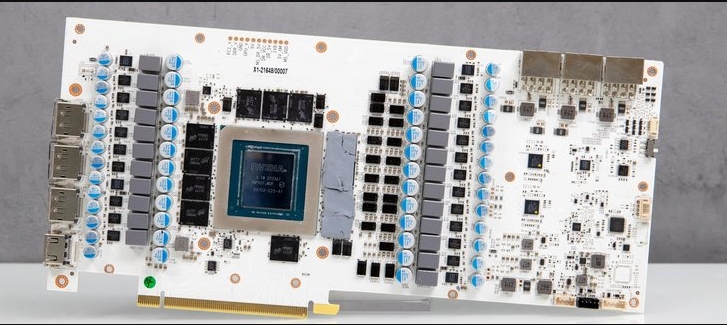

並列バスは、高帯域幅と低遅延を必要とするアプリケーションに適しています。一般的なアプリケーションには、コンピュータ内のデータ転送やグラフィックスカードなどの高性能周辺機器の接続が含まれています。並列バスは複数ビットのデータを同時に転送することができ、大量のデータを処理する際に顕著な利点があります。例えば、PCIやPCIeなどの従来のコンピュータバスは、並列性を用いて高速データ転送を行う。しかし、高動作周波数では、並列信号線間に深刻な干渉が発生する可能性があるため、設計者は並列バスを使用する際に信号整合性維持と干渉管理を考慮する必要がある。適切な配線および信号調整技術は、これらの問題の影響を効果的に低減することができる。

シリアル・バスは、パラレル・バスよりも長距離データ転送と大規模なデータ交換に優れています。シリアルバスは配線が簡単で、コストが低く、現代の通信の主流の選択肢の1つです。アプリケーションには、I 2 C、SPI、USBなどのさまざまなインタフェース規格が含まれており、センサ、マイクロコントローラ、その他の周辺デバイス間の接続に広く使用されています。シリアルバスの設計により、耐干渉性に優れ、電磁干渉が深刻な環境に適しています。例えば、CANバスは自動車や工業用途でよく使用されるシリアル通信プロトコルであり、その強力なエラー検出と冗長化メカニズムは複雑な環境での信頼性の高いデータ伝送を保証する。

一度に1つのデータしか転送できません。狭い道のように、1台の車だけが上を歩くことができます。データは次々と転送されなければならず、長いデータ列のように見えるため、「シリアル」と呼ばれています。

並列転送の最良の例は、メモリチップDDRである。DQSとDQMとともに、データ線D 0-D 7のセットがあります。このグループの回線は一緒に転送されます。どのビットにエラーがあっても、データは正しく転送されません。再送のみ。したがって、データ線の各ケーブルは長さが等しく、何度も巻き取らなければなりません。

シリアルデータが異なります。データは1つずつ転送され、ビット間には接続されていません。このビットにはエラーがなく、次のビットを転送できません。並列データはデータのセットで、1人がエラーを起こし、データセット全体が動作しなくなります。

PCB配線要件

並列バス配線の要件:

(1)バスは内部配線が望ましいことを提案し、バスと他の配線との距離はできるだけ増加しなければならない。

(2)特殊要求のほか、単線設計インピーダンスは50オーム、差分設計インピーダンスは100オームを保証する。

(3)同じグループのバスは同じ配線長を維持し、クロック線と一定のタイミング関係に従うことを提案し、タイミング解析の強い結果を参照して配線長を制御する。

(4)参照平面の完全性を確保するために、このバスのI/O電源またはGND参照平面にできるだけ近づけることをお勧めします。

(5)立上り時間が1 ns未満のバスは完全な参照平面を必要とし、パーティションを通過してはならない。

(6)より低いアドレスバス基準クロック配線要件を提案する。

(7)蛇行巻線の間隔は線幅の3倍未満であってはならない。

高速PCBシリアルバス配線要件

100 Mbps以上の周波数を有するシリアルバスについては、パラレルバスの一般的なクロストーク制御と配線規則に従うほか、配線設計においていくつかの追加の要件を考慮する必要がある:

(1)高速PCBシリアルバスは配線損失を考慮し、線幅と線長を決定する必要がある。

(2)通常の場合、線幅は5 mil以上で、配線はできるだけ短くすることを提案する。

(3)ファンアウトスルーホールを除いて、高速シリアルバスは穴を開けて交換してはならない。

(4)シリアルバスに関わる挿入ピンの速度が3.125 Gbpsより高い場合、不連続インピーダンスによる非放射影響を低減するために、半田付け防止ディスクを最適化しなければならない。

(5)高速シリアルバス配線層を交換する際に、ビアスタブが最も小さい配線層を選択することを提案する。コネクタの信号に対して、配線空間が限られている場合、短い貫通孔を有する短い断線を有する配線層は送信端に優先的に割り当てられる。

(6)速度が3.125 Gbps以上の場合、信号通過孔のそばに接地孔を掘ることを提案し、交流結合コンデンサも特殊な処理を行ってパッドを防ぐべきである。

(7)高速信号スルーホールを逆ドリル処理する場合、フローボトルネックが狭くなった後の電源接地面の電流容量減少とフィルタループインダクタンス増加の影響を考慮する必要がある。

(8)高速信号は平面層の分割線を避け、信号線エッジと分割線エッジの間の水平距離は3 Wに保証される。

(9)双方向高速信号は交差及びルーティングしてはならない。