家電用降圧スイッチング電源回路. 設計者は、この回路図において、制御信号回路12からの電力回路の構成要素を区別することができる. 設計者がデジタル回路の部品であるかのように、電源のすべての構成要素を扱う場合、問題は深刻である. これは通常、最初のパスを知る必要があります 高周波PCB 電源電流, そして、小さいシグナル制御回路および電源回路構成要素およびそれらの配線間の区別するために.

一般に、電源の電力回路は、主に、入力フィルタコンデンサ、出力フィルタコンデンサ、フィルタインダクタ、および上部および下部電力FETを含む。制御回路は、主にPWM制御チップ、バイパスコンデンサ、ブートストラップ回路、フィードバック分圧器およびフィードバック補償回路を含む。

典型的な降圧スイッチング電源回路図(12 V入力、3.3 V/15 A出力)[パワー制御回路(薄線)、パワー回路(太い線)]電源回路PCBのレイアウト

PCB上の電源装置の正しい配置および配線は、全体の電源が適切に機能するかどうか決定する。設計者は最初にスイッチング電源装置の電圧と電流の波形を理解しなければならない。

降圧スイッチング電源のパワー回路構成要素の電流波形および電圧波形を以下に示す。

入力フィルタキャパシタ(CIN)、上部MOSFET(S 1)および下側MOSFETs(S 2)を流れる電流は、高周波数およびピーク値のAC電流であるので、CIN−S 1−S 2によって形成されるループ面積を最小にする必要がある。同時に、S 2、L及び出力フィルタキャパシタ(Cout)からなるループ領域を最小化する必要がある。

スイッチング電源電流と電圧

デザイナーがこの記事で概説されるように電源回路PCBを製作しないならば、以下に示されるように間違った電源PCBを製造しそうです。

不正確なスイッチング電源装置の配置と配線

このPCBレイアウトには多くのエラーがあります。

CINの大きなESLのため、CINの高周波フィルタリング能力は、基本的に消えます;第2に、CIN - S 1 - S 2とS 2 - L - Coutループの面積が大きすぎて、生成される電磁ノイズは、電源自体と周辺回路に大きな干渉を引き起こす。第3に、Lのパッドは互いに接近しすぎており、CPが大きすぎて高周波フィルタリング機能を低下させる結果となる第4に、CEUTパッドリードが長すぎるため、ESLの高周波フィルタリング機能の損失が大きくなる。

これは、PCB配線のためのより良い電源回路です。cn‐s 1‐s 2とs 2‐l‐coutループの面積を制御した。

S 1のソースとS 2のドレインとの間の接続は、銅パッドの単一の部分である。この接続点の電圧は高周波数であるので、S 1、S 2、Lは非常に近接している必要がある。LとCoutの間の配線はピーク値を有する高周波電流を有しないが、より広い配線はDCインピーダンスの損失を減らし、電源の効率を向上させることができる。

コストが許すならば、電源は2つの側が完全に地面に接続しているPCBでありえます、しかし、注意は地面の電源と信号線を避けるためにとられなければなりません。チップコンデンサは、電源の高周波フィルタリング性能を改良するために電源の入出力ポートに添加される。

電力制御回路PCBレイアウト

電力制御回路のpcbレイアウトも非常に重要である。不合理なレイアウトは電源出力電圧ドリフトと発振の原因となる。制御線は、高周波交流ループの真ん中ではなく、電力回路の縁に配置されるべきである。バイパスコンデンサは、チップのVCCおよびGNDに近くなければならない。フィードバック分圧器抵抗器も

チップの近くのED。チップをMOSFETに駆動するループは、できるだけ短くしなければならない。

パワーレイアウトの基本的なポイント:制御チップから上部および下部のFETへの駆動回路ループは、できるだけ短くなければならない。

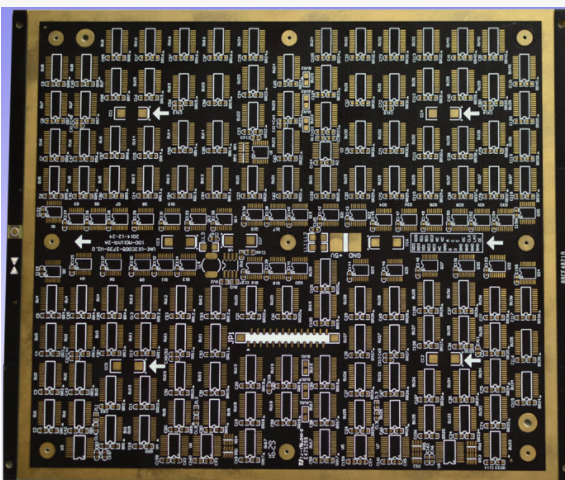

スイッチング電源のPCBレイアウト例

典型的な降圧電源のPCBコンポーネントの表面マップは、記事で参照してください。この電源には低コストPWMコントローラ(Semtech SC 1104 a)が使用される。PCBの下層は完全な接地層である。PCBパワー形成と制御形成の間には分離はない。

入力ソケット(C 1、C 2)、S 1、S 2、L 1、出力フィルタコンデンサ(C 10、C 11、C 12、C 13)を通して入力ソケット(PCBの左上)からの電源の電力回路は、出力ソケット(PCBの右下)に至るまで見られる。SC 1104 AはPCBの左下に配置される。

電力回路電流は、層20の制御回路を通過しないので, 電力回路接続から制御回路接続を分離する必要はない. 入力ソケットがPCBの左下に置かれている場合, the

8大きな取材

1. バイパスチップコンデンサのキャパシタンスは、大きすぎてはならない, そして、その寄生的な直列誘導は、できるだけ小さくなければなりません. Multiple capacitors in parallel can improve the impedance characteristics of the capacitor;

2. インダクタの寄生シャント容量は、できるだけ小さくなければならない, そして、インダクタピンとパッドの間の距離は、できるだけ遠くなければならない

層上にいかなる電力又は信号配線をも配置しないこと

高周波ループの面積をできるだけ小さくすること

5. Hole placement should not destroy the path of high frequency current on the formation;

6. システムボード上の異なる回路は異なる接地を必要とする, そして、異なる回路の接地は、単一のポイントで電源接地に接続している

電界効果管駆動回路ループの上下端に対する制御チップは、できるだけ短くすべきである

スイッチング電源回路および制御信号回路構成要素は、異なる接地層に接続する必要がある。これら2つの接地層は、一般的に1つのポイントを介して接続される