Kapensiensi parasitik sendiri bukanlah kapasitasi, menurut prinsip kapasitasi boleh diketahui, kapasitasi terdiri dari dua plat tiang dan media mengisolasi, kemudian kapasitasi parasitik tidak dapat dihindari. Kekuatan parasitik secara umum merujuk kepada ciri-ciri kapasitasi yang dipaparkan diantara angin induktor, diantara pins cip, dan diantara pins setengah konduktor kuasa pada frekuensi tinggi.

Kekuatan parasitik secara umum merujuk kepada ciri-ciri kapasitasi induktor, penahan, pin cip, dll. pada frekuensi tinggi. Sebenarnya, resistor yang sama dengan kondensator, induktor, dan siri resistor, dalam kes prestasi frekuensi rendah tidak terlalu jelas, sementara dalam kes frekuensi tinggi, nilai yang sama akan meningkat, tidak boleh diabaikan. Dalam pengiraan kita perlu mempertimbangkan. ESL adalah induktan yang sama, ESR adalah resisten yang sama. Sama ada ia adalah resistensi, kapasitasi, induktansi, atau dioda, transistor, tabung MOS, dan ICs, kita perlu mempertimbangkan kapasitasi dan induktansi yang sama dalam kes frekuensi tinggi.

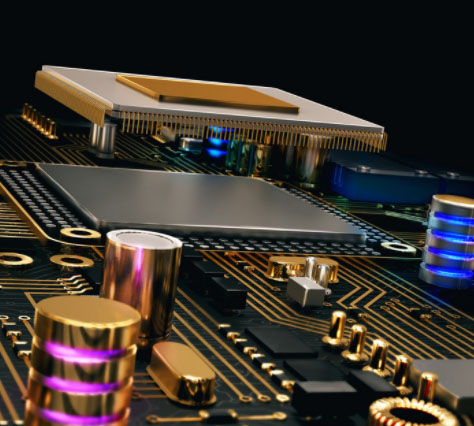

Papan PCB terdiri dari konduktor berbilang yang disambung secara paralel, seperti jejak, dipisahkan oleh pengisih. Jejak ini bersama dengan bahan dielektrik membentuk kondensator, yang menghasilkan kondensasi parasit yang tidak diinginkan atau kesan kondensasi yang hilang.

Elemen parasit dalam PCB mungkin kapasitas parasit, resistensi parasit, dan inductans parasit. Apabila jejak dekat, kesan kapasitasi parasit sangat terkenal dalam papan frekuensi tinggi. Kesan ini tidak diperlukan dan akan mempengaruhi fungsi peranti. Ia boleh menyebabkan masalah seperti crosstalk, EMI, dan integriti isyarat. Penjana PCB yang berurusan dengan papan frekuensi tinggi, kadar data tinggi, dan isyarat-campuran mesti mempertimbangkan kapasitasi parasit dan kesan induktan bila merancang bentangan PCB.

Kapensiensi parasitik adalah karakteristik kandungan konduktor. Ia adalah jumlah penyimpanan per unit perubahan potensi. Formula pengiraan kapasitas parasit ialah C= q/v. Di mana C ialah kapasitas dalam farad, v ialah tensi dalam volts, dan q ialah muatan dalam coulombs.

Untuk isyarat elektrik konstan yang tidak berubah dengan masa, dv/dt = 0, yang bermakna tiada perubahan dalam potensi; Jadi, i = 0.

Jika terdapat kondensator dalam loop sirkuit, dv/dt akan menuju ke nilai tetap, iaitu perubahan potensi dan semasa dijana; Jadi, ia adalah.

Kiraan kapasitas jejak

Kapansansi kondensator plat selari diberikan oleh C= (kA/11.3d)pF. Di mana C ialah kondensansi, A ialah kawasan plat dalam cm 2, k ialah relativiti kebenaran bahan plat, dan d ialah jarak antara plat dalam cm.

Modeling komponen parasit PCB pada frekuensi tinggi.

Kesan kapasitasi parasit adalah masalah dalam papan sirkuit frekuensi tinggi. Dalam operasi frekuensi rendah, komponen parasit boleh diabaikan kerana ia tidak benar-benar akan mempengaruhi fungsi sistem. Setiap pad pada papan sirkuit mempunyai kapasitas parasitik, dan setiap jejak mempunyai induksi parasitik. Pad juga meningkatkan resistensi parasit, yang menyebabkan kehilangan IR. Kekuatan parasitik mungkin wujud diantara PCB, papan kosong, PCBA, papan pemasangan, dan konduktor dalam pakej komponen, terutama peranti lekap permukaan (SMD).

Oleh kerana plat kondensator dalam mempunyai perbezaan potensi, ada peluang untuk arus. Tidak penting sama ada muatan disimpan diantara plat kondensator; semasa tidak akan mengalir sehingga terdapat perbezaan potensi. Apabila perbezaan potensi ini meningkat, penurunan aliran elektron ke muatan yang sepadan boleh diperhatikan untuk laluan isyarat yang diinginkan yang mempengaruhi integriti isyarat secara negatif.

Apa perbezaan antara kapasitasi tersesat dan kapasitasi parasit?

Terma kapasitasi hilang sering digunakan secara bertukar dengan kapasitasi parasit. Namun, kapasitas parasit menunjukkan bahawa ia akan menghalang operasi sirkuit, dan kapasitas tersesat menunjukkan bagaimana untuk memperkenalkan kapasitas tidak diinginkan.

Apa itu kapasitasi yang sesat?

Sebab kapasitasi maya yang terbentuk antara dua konduktor PCB dan sebab pengaruh persekitaran sekitar, kapasitasi hilang tidak sentiasa dikesan. Oleh itu, ia dipanggil kapasitasi yang sesat.

Apa resistensi parasit dalam PCB?

Keperlawanan parasitik disambung dalam siri sepanjang jejak atau wujud sebagai shunts antara unsur konduktif.

Apa induksi parasit dalam PCB?

Induktan parasitik wujud sepanjang jejak, menunjukkan perilaku penyimpanan dan penyebaran tenaga elektrik, sama seperti induktor sebenar. Semua konduktor adalah induktif, dan pada frekuensi tinggi, induktif walaupun wayar relatif pendek atau jejak PCB boleh menjadi penting.

Kesan kapasitasi parasitik boleh menjadi saling bercakap dan bunyi, balas balik yang buruk dari output, dan bentuk sirkuit resonan. Oleh itu, perhatian mesti diberikan kepada rancangan PCB keseluruhan, terutama bentangan. Apabila meletakkan konduktor di sebelah konduktor lain, layout yang baik harus dilakukan dengan hati-hati ekstrim.

Elemen parasitik termasuk induktan bentuk oleh petunjuk pakej, jejak panjang, pad-ke-tanah, pad-ke-kuasa pesawat, dan pad-ke-baris kondensator, termasuk interaksi dengan vias. Memahami unsur parasit sebagai unsur parasit, yang mengancam prestasi sirkuit anda. Tidak diinginkan dan tidak dapat dihindari, tetapi pada masa yang sama boleh dikawal.

Dalam sirkuit kelajuan tinggi, beberapa persepuluh picofarad cukup untuk mempengaruhi prestasi sirkuit. Contohnya, kapasitas parasit 1pF pada input terbalik akan menyebabkan puncak 2dB dalam domain frekuensi. Jika ia melebihi 1pF, ia akan menyebabkan ketidakstabilan dan oscilasi.

Kapasitor menghalang isyarat frekuensi rendah dan DC dan lulus isyarat frekuensi tinggi dalam sirkuit elektronik. Karakteristik ini bagi kondensator yang melalui isyarat frekuensi tinggi (kelajuan yang mana pembuangan kondensator adalah sebab lain mereka digunakan untuk menggantikan bateri yang lebih lambat) adalah sebab masalah kondensasi hilang dalam sirkuit kelajuan tinggi. Untuk konduktor, kapasitasi tersesat boleh memperkenalkan EMI atau bunyi, yang boleh menyebar sepanjang wayar dan kabel atau dipindahkan ke jejak dekat. Biasanya, mustahil untuk menghapuskan kapasitasi yang hilang. Namun, ada beberapa kaedah yang berkesan untuk mengurangi situasi ini pada tahap bentangan PCB.

Lupakan laluan selari: Apabila laluan selari, terdapat kawasan terbesar diantara dua logam, jadi terdapat kapasitasi terbesar diantara mereka.