Artikel ini memperkenalkan tiga cip penyulitan umum untuk menilai format fail dari suffiks fail PCB dan mencegah penyulitan PCB.

Hakim format fail dari suffiks fail PCB

Banyak kawan sering bertemu fail reka PCB berbeza format dalam proses kerja. Artikel ini mengungkapkan format yang sepadan dengan tambahan fail. Saya harap ia akan membantu semua orang.

1. PCB. Suksi yang paling umum, banyak fail reka PCB adalah suai ini, yang paling umum adalah Protel, PADS, tambahan kepada Cadstar ZUKEN, CR5000, P-CAD Altimum, dll.

2.brd. Cadence Allegro, Eagle.

3.max. Perisian reka PCB ORCAD dari Cadence Company.

4.min. Output fail teks oleh ORCAD.

5. PCBdoc. Dirancang oleh versi baru Protel DXP dan AD6.

6.asc. Format teks bagi beberapa perisian PCB, seperti PADS,protel,P-cad,dll.

7.dat, .neu, .net, dll. Fail Netrual yang dijana oleh Mentor.

8. Ia terdiri dari banyak folder. Salah satunya ialah centlib (pustaka pusat), fail desain ekspedisi mentor.

9.cam. CAM350 atau fail Camtastic 2000.

10.tgz. Fail ODB++ dijana oleh fail reka PCB.

11.cad. Fail Gencad dijana oleh fail reka PCB.

Tiga cip penyulitan umum untuk mencegah penyulitan PCB

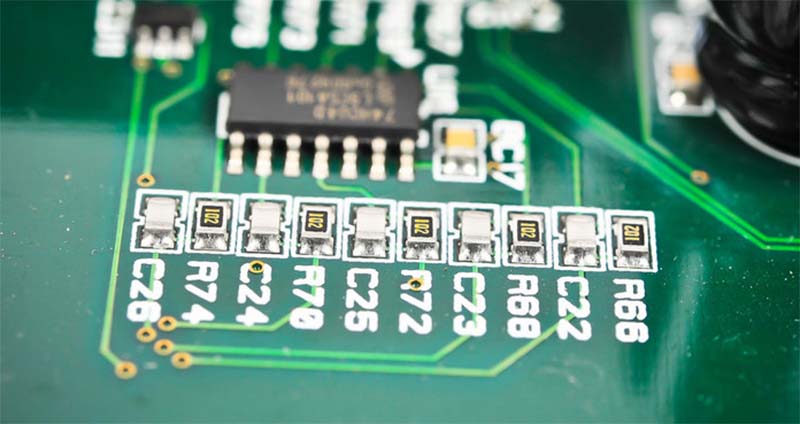

Dalam industri produk teknologi elektronik dan maklumat yang sangat kompetitif, cip penyulitan semakin penting untuk produk tertentu dengan biaya pembangunan yang lebih tinggi untuk mencegah salinan rakan. Ini tiga cip penyulitan umum

Solution 1:PCB copy board logic encryption chip

Struktur Chip:EEPROM + litar logik

Skema perlindungan hak cipta: pengesahihan kata laluan, pengesahihan algoritma simetrik

Keuntungan:biaya rendah, sirkuit periferik sederhana, pembangunan sederhana

Kegagalan:keselamatan rendah dan mudah untuk diselesaikan

Pilihan 2:Transplant encryption chip based on algorithm

Struktur Chip: cip penyulitan grad keuangan-keselamatan tinggi

Skema perlindungan hak cipta:

1.Solusi utama: pemindahan algoritma, pemindahan sebahagian dari program MCU ke cip penyulitan untuk dijalankan

2.Skema bantuan: pengesahihan algoritma simetrik

Keuntungan:keselamatan tinggi, MCU tidak boleh mengelak cip penyulitan untuk berjalan secara independen.

Kegagalan: kos tinggi, muatan kerja pengguna meningkat, pengguna perlu mengembangkan program cip keselamatan, dan persekitaran program muat turun perlu ditetapkan semasa produksi mass a.

Skema 3:Cip penyulitan berdasarkan sistem pengesahihan PKI

Struktur Chip: cip penyulitan grad keuangan-keselamatan tinggi

Skema perlindungan hak cipta:

1.Berdasarkan pengesahihan keselamatan tinggi sistem PKI, kunci peribadi disimpan dalam cip keselamatan, yang dilindungi oleh perkakasan dan tidak dapat dibaca, dan kunci setiap cip berbeza.

2.Data kunci papan salinan PCB disimpan dan dibaca tersulit.

Keuntungan:keselamatan tinggi, kunci peribadi disimpan dalam cip keselamatan, perlindungan perkakasan, tidak dapat dibaca, dan setiap cip mempunyai kunci yang berbeza. Cip keselamatan menyediakan API, jadi pengguna tidak perlu mengembangkan program cip keselamatan.

Kegagalan:biaya lebih tinggi