Kawalan kad PCI lebih indah, yang ditentukan oleh ciri-ciri isyarat PCI. Dalam rekaan papan sirkuit PCB digital frekuensi tinggi konvensional, kita sentiasa berusaha untuk menghindari refleksi isyarat, overshoot, ringing, dan fenomena bukan-monotonik disebabkan oleh ketidaksepadan impedance. Namun, isyarat PCI menggunakan prinsip refleksi isyarat untuk menghantar isyarat fizikal, untuk membuat penggunaan yang masuk akal refleksi isyarat semasa cuba untuk menghindari kesan sampingan seperti overshoot besar, bunyi dan non-monotonicity, PCI-SIG telah membuat beberapa persediaan mengenai penyelesaian fizikal PCB dalam spesifikasi PCI.

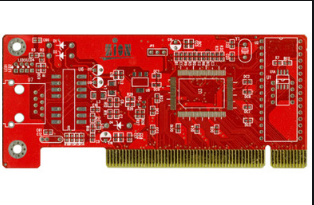

PCI-SIG menyarankan penggunaan papan PCB empat lapisan untuk kad PCI. Penghapusan isyarat bagi sambungan PCI yang dinyatakan oleh PCI-SIG juga dipeptimalkan untuk kesehatan kabel papan empat lapisan. PCI-SIG juga telah membuat diagram skematik direkomendasikan untuk distribusi pin pengawal PCI. Malah, penghasil pengendali PCI seperti AMCC, PLX, dan OXFORD juga melaksanakan rekomendasi ini. Di bawah distribusi pin yang direkomendasikan ini, dua lapisan digunakan. Papan PCB sebenarnya sangat selesa untuk kawat, tetapi jika perkakasan sistem kad PCI sangat kompleks dan memerlukan tahap pembahagian kuasa berbilang, lebih baik untuk mempunyai PCB berbilang lapisan.

Setiap isyarat PCI pada kad PCI hanya boleh disambung ke satu muatan (termasuk juga tidak boleh disambung ke resistor tarik-up). Kecuali CLK, RST, INTA#~INTD#, JTAG pins ini, semua pins dari titik kenalan jari emas dan soket kad hingga akhir muatan tidak boleh lebih besar dari 1.5 inci; panjang isyarat CLK adalah 2.5 +-0.1 inci, panjang ini agak panjang, jadi dalam banyak kes ia perlu dijalurkan sekitar untuk memenuhi keperluan panjang. Inilah sebabnya anda sering melihat jejak ular CLK pada kad PCI; tiada peraturan istimewa untuk pins yang tersisa. Apabila menggunakan PCB berbilang lapisan, jejak isyarat tidak sepatutnya menyeberangi aras kuasa yang berbeza (sekurang-kurangnya, lapisan dengan aras kuasa pecahan sepatutnya berada di sisi lain PCB), sebab itulah kita sering melihat semua jari emas di sisi A kad PCI muncul sebab isyarat sering pergi ke sisi B (sisi komponen) melalui lubang.

Impedansi karakteristik setiap isyarat PCI adalah 60-100 ohms, dan kapasitasi muatan tidak boleh melebihi 10pf. Pad IO IC sepatutnya dapat menahan -3.5V bawah tanah dan +7.1V isyarat melebihi. Bagi penghasil pengendali PCI seperti AMCC, PLX, dan OXFORD, pengendali IC memenuhi peraturan ini, dan pengguna tidak perlu mempertimbangkannya. Namun, jika anda menggunakan CPLD/FPGA untuk melaksanakan pengendali PCI, anda mesti mempertimbangkan sama ada model yang digunakan memenuhi peraturan ini. Pembuat CPLD/FPGA seperti Altera dan Xilinx akan jelas dinyatakan dalam manual data mereka sama ada CPLD/FPGA serasi dengan spesifikasi isyarat PCI.

Kawalan kad PCI 32-bit 33MHz biasa adalah relatif mudah, terutama untuk memenuhi keperluan panjang. Sebenarnya, jika anda tidak mengikut keperluan kawat secara ketat, umumnya tidak akan ada masalah, tetapi bergantung pada set cip papan ibu, apabila masalah kesesuaian isyarat berlaku, penyahpepijatan perkakasan kad PCI akan menjadi pengalaman yang paling menyakitkan dalam desain sirkuit PCB. .