スイッチング電源のスイッチング特性により, スイッチング電源が大きな電磁両立性干渉を生じさせる原因は容易である. 電源エンジニアとして, 電磁両立技師, または PCB基板レイアウト エンジニア, 電磁両立性問題の原因を理解し、対策を講じなければならない, 特にレイアウトエンジニア, 汚れたスポットの拡大を避ける方法を理解する必要があります, this article mainly introduces

The main points of the power supply PCBボード デザインについて.

29レイアウトと PCBボード

1. いくつかの基本原則:任意のワイヤインピーダンスがあります電流は常に自動的にインピーダンスの経路を選択する放射強度は電流に関係している, 頻度, ループ領域;コモンモード干渉は大きなDVの相互キャパシタンスに関係する/地面にDT信号EMIを減らし、干渉防止能力を高める原理は同様である.

2. レイアウトは電源によって分割されるべきである, アナログ, 高速ディジタルおよび各機能ブロック.

3. 大きなdiの面積を最小にする/DT loop and reduce the length (or area, 大きなDVの幅/DT signal line). トレース面積の増加は、分布キャパシタンスを増加させる. 一般的なアプローチは:トレースの幅をできるだけ大きくしようとする, but remove the excess part), そして、直線で歩くようにしなさい, 放射線を減らすためにその隠れた囲まれた地域を減らしてください.

4. 誘導性クロストークは主に大きなdi/dt loop (loop antenna), 誘導強度は相互インダクタンスに比例する, so it is more important to reduce the mutual inductance with these signals (the main way is to reduce the loop area and increase the distance); Sexual crosstalk is mainly generated by large dv/DT信号, そして、誘導強度は相互キャパシタンスに比例する. All decrease the mutual capacitance with these signals (the main way is to reduce the effective coupling area and increase the distance. 距離が増加すると相互キャパシタンスは減少する. Faster) is more critical.

5. 可能な限りループキャンセルの原理を使用して, さらに大きなダイの面積を小さくする/dt loops (similar to twisted pair, use the principle of loop cancellation to improve anti-interference ability and increase transmission distance).

6. ループ面積を減らすことは放射線を減らすだけではない, ループインダクタンス, 回路性能の改善.

7. ループ面積を減らすためには、各トレースの戻りパスを設計する必要がある.

8. 時 複数 PCBボード コネクタを介して接続する, また、ループ面積の到達を考慮する必要がある, 特に大きいdiのために/DT信号, 高周波信号または敏感な信号. 信号線は接地線に相当する, そして、2本のワイヤーは、できるだけ近いです. 必要なら, twisted pair wires can be used to connect (the length of each twisted pair wire corresponds to an integer 複数 of the noise half-wavelength). あなたがコンピュータケースを開くならば, マザーボードからフロントパネルへのUSBインターフェースはツイストペアケーブルで接続されていることがわかります. ツイストペア接続は、干渉防止および放射線低減に重要である.

9. データケーブル用, ケーブルでより多くの接地線を配置しようとする, そして、これらの接地線をケーブルに均等に分配させる, ループ面積を効果的に低減できる.

10. いくつかのボード間接続線は低周波信号である, because these low-frequency signals contain a lot of high-frequency noise (through conduction and radiation), 彼らが適切に扱われないならば、これらの雑音を放射するのは簡単です.

11. 配線, まず放射線が発生しやすい高電流トレースとトレースを考える.

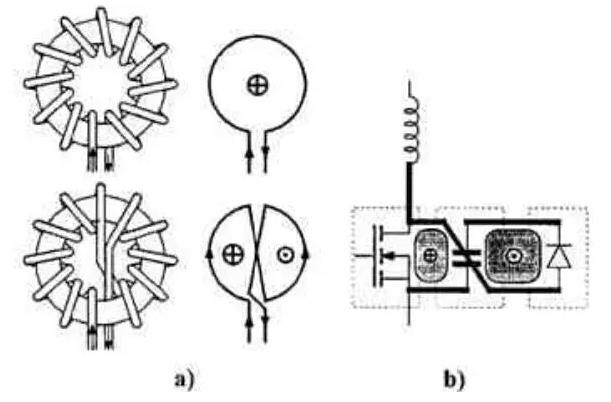

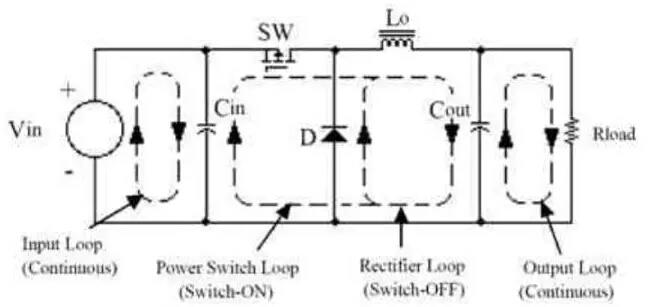

12. スイッチング電源は通常4つの電流ループを有する, 出力, スイッチ, フリーホイール. その中で, 入出力電流ループは、ほぼ直流電流である, ほとんどEMIが発生しない, しかし、彼らは簡単に邪魔されますスイッチングおよびフリーホイール電流ループは、より大きいdiを有する/dt, 注意が必要.

13. The gate drive circuit of the mos (igbt) tube usually also contains a large di/dt.

14. 小さな信号回路を配置しない, 制御とアナログ回路のような, 大電流内, 干渉を避けるための高周波高電圧回路.

15. Reduce the susceptible (sensitive) signal loop area and trace length to reduce interference.

16. 小さい信号痕跡は大きなDVから遠く離れている/DT信号 lines (such as the C pole or D pole of the switch tube, buffer (snubber) and clamp network) to reduce coupling, and ground (or power supply, 要するに, often Potential signal) to further reduce the coupling, 地面は地面との良好な接触であるべきである. 同時に, 小さい信号痕跡は、大きいdiからできるだけ遠くでなければなりません/誘導クロストークを防ぐDT信号線. 大きなDVの下で小さな信号を追跡しないでください/dt signal. If the back of the small signal traces can be grounded (the same ground), これに結合されたノイズ信号も低減することができる.

17. より良いアプローチは地面を、そして、これらの大きなDVの後ろに置くことです/DTとDI/DT信号トレース (including the C/D poles of the switching devices and the switch tube heat sink), そして、接地のために上下層を使用する. 接続スルーホール, and connect this ground to a common ground point (usually the E/スイッチチューブのS極, or sampling resistor) with a low-impedance trace. これは放射線EMI. 小信号グランドはこのシールドグラウンドに接続してはならないことに留意すべきである, さもなければ、それはより大きな干渉を導入するでしょう. 大きなDV/DTトレースは、通常、相互キャパシタンスを通してラジエータと近くのグラウンドに干渉を結合する. スイッチチューブラジエータをシールドグランドに接続します. 表面実装スイッチングデバイスの使用は相互キャパシタンスも低減する, これによりカップリングを低減する.

18. 干渉する傾向がある跡のためにビアを使わないでください, ビアが通過するすべての層に干渉するので.

19. シールドは放射EMIを減らす, しかし、地上への増加した静電容量のため, conducted EMI (common mode, or extrinsic differential mode) will increase, しかし、シールド層が適切に接地される限り, あまり増加しない . それは、実際のデザインで秤量され、考慮することができます.

20. 共通インピーダンス干渉を防ぐ, ワンポイント接地と電源を1点から使用.

21. スイッチング電源は通常3つのグラウンドを有する, 出力高電流グラウンド, 小信号制御グラウンド. The ground connection method is shown in the following diagram:

22. 接地時, 地面の性質をまず判断する, 接続を行う. サンプリングおよびエラー増幅のためのグラウンドは、通常出力キャパシタの負極に接続されるべきである. サンプリング信号は、通常出力キャパシタの正極から取り出されるべきである. 共通インピーダンス干渉. 通常、ICの制御グラウンドとドライブグラウンドは別々に導出されない. この時に, 上記の接地に対するサンプリング抵抗器のリードインピーダンスは、共通インピーダンス干渉を低減し、電流サンプリングの精度を改善するために、できるだけ小さくなければならない.

23出力電圧サンプリングネットワークは、出力の代わりにエラー増幅器に近い. これは、低インピーダンス信号が高インピーダンス信号よりも干渉を受けにくいためである. サンプリングトレースは、ピックアップされたノイズを低減するために、できるだけ近いものでなければならない.

24. 相互インダクタンスを減少させるために、互いに遠ざかって垂直になるインダクタンスのレイアウトに注意を払う, 特にエネルギー蓄積インダクタンスとフィルタインダクタンス.

25. 高周波コンデンサと低周波コンデンサを並列に使用する場合のレイアウトに注意を払う, そして、高周波コンデンサはユーザーに近い.

26. Low-frequency interference is generally differential mode (below 1M), そして、高周波干渉は、一般にコモンモードである, 通常放射線と結合する.

27. 高周波信号が入力リード線に連結される, it is easy to form EMI (common mode). 電源リングの近くに入力リードに磁気リングを置くことができます. EMIが減少するならば, この問題を示す. この問題の解決策は、結合を減少させたり、回路100のEMIを減少させることである. 高周波ノイズがきれいに濾過されていないならば、入力鉛に導通してください, EMI (differential mode) will also be formed. この時に, 磁気リングは問題を解決できない. String two high-frequency inductors (symmetrical) where the input lead is close to the power supply. 減少は、この問題が存在することを示します. この問題を解決する方法は, またはバッファリングによる高周波ノイズの発生を減らすために, 締付け等.

28. 差動モードとコモンモード電流の測定.

29. EMIフィルタは、受信ラインに可能な限り近くなければなりません, そして、EMIフィルタの前後のステージの間の結合を最小にするために、入って来るラインのルーティングはできるだけ短くなければなりません. The incoming line is shielded with the chassis ground (the method is as described above). 出力EMIフィルタは同様に扱われるべきです. 入力ラインと高dvの間の距離を増やすためにしてください/dt signal traces, これは PCBボード layout.