Al giorno d'oggi, la tecnologia CMOS consente a un dispositivo FPGA di avere più interfacce I/O. Allo stesso tempo, negli ultimi anni, il basso consumo energetico ha iniziato a diventare il concetto principale delle interfacce I/O ad alta velocità. Il modo più efficace per ridurre il consumo energetico è quello di ridurre la tensione e la riduzione della tensione si tradurrà in un margine di rumore più piccolo consentito dall'interfaccia I/O. Pertanto, è molto necessario per gli utenti FPGA quantificare il rumore di commutazione sincrona a livello di sistema (SSN) nell'ambiente chip, pacchetto e PCB.

Questo articolo introduce sistematicamente SSN, concentrandosi sull'SSN causato dal buffering dell'output FPGA. Questo tipo di rumore è generalmente chiamato Sincronic Switching Output Noise (SSO), che è diverso da SSN causato dal buffering in ingresso. Questo articolo introduce le cause dell'SSO a livello di sistema e propone un metodo di modellazione SSO a livello di sistema stratificato. Allo stesso tempo, questo articolo spiega anche come associare il modello SSO alle misurazioni del dominio di frequenza e del dominio temporale e fornisce diversi metodi di progettazione PCB per ridurre l'SSO.

Il meccanismo di formazione dell'SSO a livello di sistema

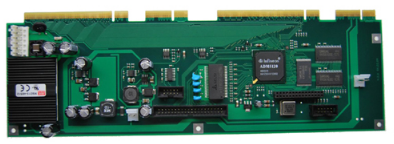

Un PCB con FPGA è un sistema complesso che può essere diviso in una parte chip contenente circuiti attivi, una parte di pacchetto con componenti passivi incorporati che supportano tracce e una parte di circuito che fornisce collegamenti tra FPGA e l'esterno. In questo tipo di sistema, è difficile capire le caratteristiche del rumore all'interno del chip. Pertanto, è molto utile quantificare l'SSO alle estremità vicine e lontane delle tracce PCB collegate all'FPGA. Ci sono due fattori principali che causano SSO: l'impedenza della rete di distribuzione dell'energia (PDN) e l'accoppiamento di induttanza reciproca tra l'I/O dello switch.

Dal punto di vista del sistema, PDN include componenti a livello wafer, a livello di pacchetto e a livello di scheda, che insieme forniscono energia per i circuiti CMOS. Quando un certo numero di circuiti di azionamento di uscita CMOS è acceso contemporaneamente, una grande corrente fluirà istantaneamente negli elementi del circuito induttivo del PDN, con conseguente caduta di tensione delta-I. Le strutture di interconnessione generano induttanze parassitarie, come le sfere di saldatura di potere sul pacchetto della griglia di sfere e i vias di alimentazione nel PCB. Questa corrente che cambia rapidamente eccita anche le onde elettromagnetiche radiali tra la coppia di piano potenza/terra. Le onde elettromagnetiche vengono riflesse dal bordo planare del PCB, creando risonanza tra il piano di potenza / terra e causando fluttuazioni di tensione.

Un'altra causa importante di SSO è l'accoppiamento reciproco dell'induttanza, in particolare l'accoppiamento reciproco dell'induttanza intorno al pacchetto del chip/bordo del PCB. Le sfere di saldatura sul pacchetto BGA chip e le vie sul PCB appartengono a una struttura multi-filo strettamente accoppiata. Ogni sfera di saldatura I/O e il relativo PCB corrispondente tramite e la sua sfera di saldatura a terra più vicina e messa a terra formano un ciclo chiuso. Quando lo stato di più porte I/O cambia contemporaneamente, correnti I/O transitorie scorrono attraverso questi loop di segnale. Questa corrente di I/O transitoria genererà un campo magnetico variabile nel tempo, che invade loop di segnale adiacenti e provoca rumore di tensione indotto.

Un eccellente modello SSO dovrebbe essere in grado di riflettere il meccanismo di formazione di base di SSO. Un modello stratificato per prevedere SSO nei PCB. A livello di chip, quello di cui abbiamo bisogno è un modello buffer di uscita in grado di fornire una distribuzione accurata della corrente su linee elettriche e linee di segnale con complessità limitata. A livello di imballaggio, per semplicità, gli strumenti di modellazione possono essere utilizzati per ottenere il modello PDN e il modello di accoppiamento del segnale, ma l'interazione tra il PDN e il modello di accoppiamento del segnale deve essere attentamente considerata. Questi due modelli fungono da ponte, collegando il modello buffer di uscita all'estremità del bump del pacchetto chip e il modello a livello PCB all'estremità della sfera di saldatura. Il modello PDN del PCB di solito include il piano di potenza/massa e i condensatori di grande capacità/disaccoppiamento su di esso, mentre il modello di accoppiamento del segnale del PCB include una matrice strettamente accoppiata e tracce di segnale liberamente accoppiate su diversi strati di segnale. L'effetto di interazione di questi due modelli a livello PCB appare nel PCB tramite array. È da qui che il crosstalk induttivo porta rumore nel modello PDN, e il rumore delta-I a sua volta riduce la qualità del segnale I/O. Questo metodo di modellazione gerarchica mantiene ragionevolmente l'accuratezza della simulazione e allo stesso tempo migliora l'efficienza computazionale di tali sistemi complessi.