In modern electronic design, PCB design is crucial, and the bus, as a key channel for communication between various devices, provides the basis for the performance and efficiency of PCB design. In this article, we will discuss in depth the characteristics, advantages and disadvantages, as well as application scenarios of parallel and serial buses in high-speed PCB design, to help design engineers better understand and choose the right type of bus.

A bus is a shared physical pathway for communication between two or more devices, a collection of signal lines, and a common link between multiple components for transferring information between them. There are two main types of buses based on their mode of operation: parallel buses and serial buses.

Parallel buses are designed to allow multiple bits of data to be transmitted at the same time. This bus structure is similar to a spacious roadway that can accommodate multiple vehicles traveling at the same time, and is typically used in situations where data transmission is more demanding. The advantage of a parallel bus is that data transmission is fast because multiple signals can be transmitted at the same time. However, as data transmission rates increase, signal integrity and interference issues emerge. Parallel bus connections require more signal lines, leading to increased design complexity, and crosstalk and delay issues between signals cannot be ignored in high-frequency operations.

Unlike parallel buses, serial buses transmit data one after the other in bit order. Serial signaling typically uses fewer signal wires, which makes wiring simpler and clearer. Since only one or several wires are needed for data transmission, serial buses are especially important in reducing the amount of space taken up on the PCB and reducing the complexity of the finished product.

Serial buses are generally more resistant to interference, especially if differential signals are used, where each pair of differential wires consists of a positive and a negative, improving signal integrity. Although serial buses transmit fewer bits per unit of time, higher data rates can be achieved by using higher propagation rates.

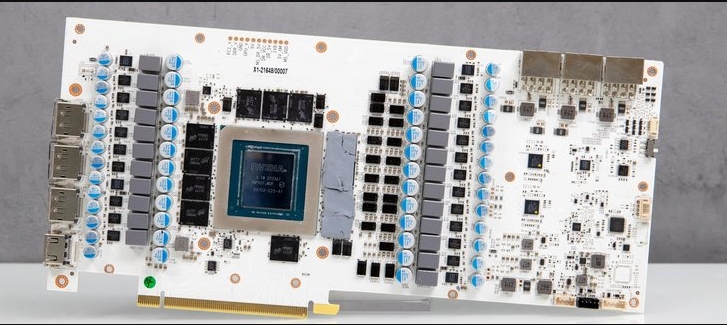

Parallel buses are suitable for applications that require high bandwidth and low latency. Common applications include the transfer of data within a computer and the connection of high-performance peripherals such as graphics cards. Parallel buses are capable of transferring multiple bits of data at the same time, which gives them a significant advantage when dealing with large amounts of data. For example, traditional computer buses such as PCI and PCIe use parallelism for fast data transfer. However, at high operating frequencies, serious interference can occur between parallel signal lines, so designers need to consider signal integrity maintenance and interference management when using parallel buses. Proper cabling and signal conditioning techniques can be effective in minimizing the effects of these problems.

Compared to parallel buses, serial buses perform better for long-distance data transmission and large-scale data exchange. With simple cabling and low cost, serial buses are one of the mainstream choices for modern communications. Applications include various interface standards such as I2C, SPI, and USB, which are widely used for connectivity between sensors, microcontrollers, and other peripherals. The design of the serial bus gives it an advantage in terms of immunity to interference, making it suitable for use in environments with heavy electromagnetic interference. For example, CAN bus is a common serial communication protocol used in automotive and industrial applications, and its robust error detection and redundancy mechanisms ensure reliable data transmission in complex environments.

Only one piece of data can be transmitted at the same time, which is like a narrow road that only allows one car to walk on. The data must be transmitted one after another, which looks like a long data string, so it is called "serial".

The best example of parallel transmission is the memory chip DDR. It has a set of data lines D0-D7, plus DQS and DQM. This set of lines is transmitted together. No matter which bit has an error, the data will not be transmitted correctly. Only retransmit. Therefore, each cable of the data cable must be of equal length, and it must be wound several times.

Serial data is different. Data is transmitted one by one, and there is no connection between bits. There is no error in this bit and the next bit cannot be transmitted. Parallel data is a set of data where one bit is wrong, and the entire set of data will not work.

PCB wiring requirements

Parallel bus wiring requirements:

(1) It is recommended that the bus is preferably internally wired, and the distance between the bus and other wiring should be increased as much as possible.

(2) In addition to special requirements, the single-line design impedance is guaranteed to be 50 ohms, and the differential design impedance is guaranteed to be 100 ohms.

(3) It is recommended that the same group of buses maintain the same length of wiring, and follow a certain timing relationship with the clock line, and control the wiring length with reference to the strong results of timing analysis.

(4) It is recommended to be as close as possible to the I/O power supply or GND reference plane of this group of buses to ensure the integrity of the reference plane.

(5) A bus with a rise time of less than 1ns requires a complete reference plane and must not cross the partition.

(6) It is recommended that the lower address bus refer to the clock wiring requirements.

(7) The spacing of the serpentine winding wire shall not be less than 3 times the line width.

High-speed PCB serial bus wiring requirements

For a serial bus with a frequency higher than 100Mbps, in addition to following the general crosstalk control and wiring rules for parallel buses, some additional requirements need to be considered in the wiring design:

(1) The high speed PCB serial bus needs to consider the loss of wiring and determine the line width and line length.

(2) It is recommended that the line width is not less than 5mil under normal circumstances, and the wiring should be as short as possible.

(3) Except for the Fanout vias, the high-speed serial bus should not be punched and changed.

(4) When the speed of plug-in pins involved in the serial bus is above 3.125Gbps, the anti-pad should be optimized to reduce the impact of non-radiation caused by discontinuous impedance.

(5) It is recommended that when changing layers of high-speed serial bus wiring, choose the wiring layer with the smallest via stub. For the signal to the connector, when the wiring space is limited, the wiring layer with the short via stub is preferentially allocated to the sending end.

(6) It is recommended that when the rate is 3.125Gbps or above, a ground hole should be drilled next to the signal via, and the AC coupling capacitor should also be specially treated for the anti-pad.

(7) If the high-speed signal vias are processed by back drilling, it is necessary to consider the influence of the reduction of the current flow capacity of the power ground plane and the increase of the filter loop inductance after the flow bottleneck is narrowed.

(8) The high-speed signal avoids the dividing line of the plane layer, and the horizontal distance between the edge of the signal line and the edge of the dividing line is guaranteed to be 3W.

(9) High-speed signals in both directions should not be crossed and routed.