PCB基板端子のマッチング技術では、比較的長いトレース(2インチ以上)の場合、その効果は他の伝送線路と同様である。伝送線路の条件を満たしているかどうかを判断するには、次のような経験式がある。

(トレース長インチ) x 0.144 >(レベル移行立ち上がり/立ち下がり時間ns )/ 2

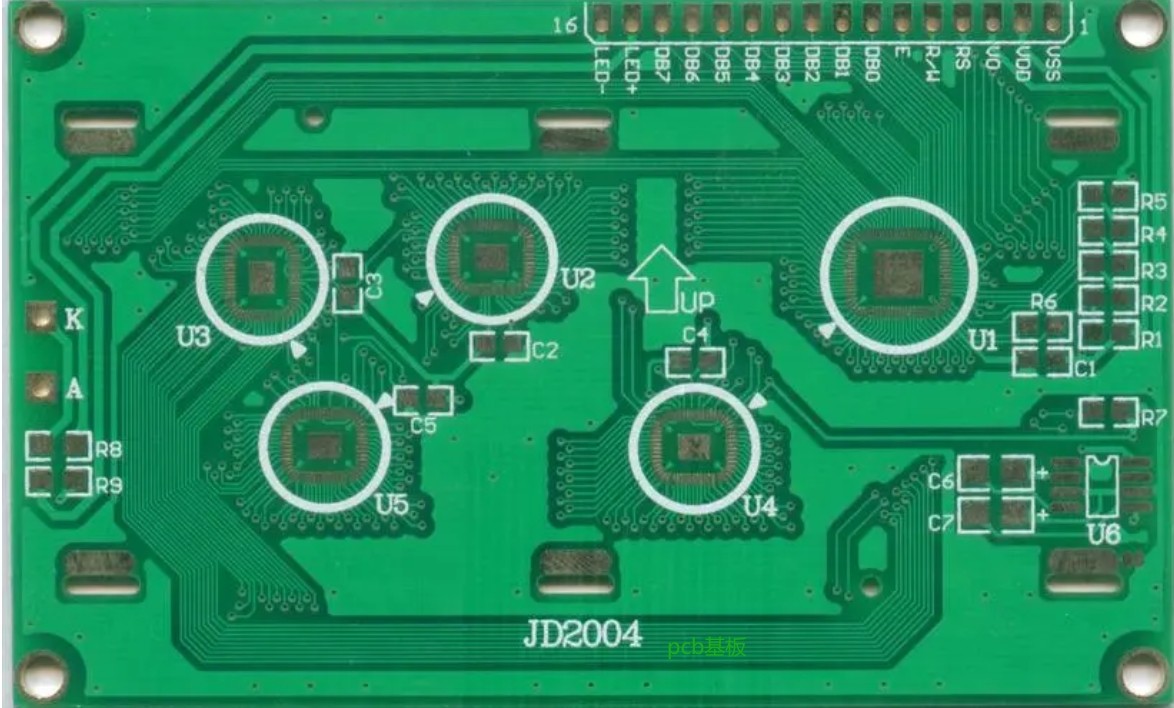

その中で、0.144/インチは、一般的なエポキシガラスクロスベース(fr 4)のPCB基板に適した伝送遅延係数である。

伝送線路が完全に整合されていない場合、すなわちRT(端子整合インピーダンス)である場合には、伝送線路特性インピーダンスである。このとき、ソースと負荷との間の多重反射は、複数のリンギング(リンギング)を引き起こす。伝送線路が完全に一致した場合、すなわち、Rt=Z 0であれば、このときリンギングはない.8インチより長いケーブルは、端末で照合されるべきです。以下のようなマッチング方法があります。

その中でもac終了は他のマッチング法より良いマッチング法である。このマッチング方法は、駆動源の負荷を増加させず、電源の負担を増大させない。

端子整合技術は最も簡単で、最も効果的な高速PCB基板設計技術である。端子整合技術を合理的に使用することで、効果的に信号の反射と信号のリンギングを低減し、信号のタイミングマージンとノイズマージンを大幅に改善し、製品の耐障害性を向上させることができます。シングルエンド信号の端子整合技術には通常、動作端のシリアル接続の端子整合技術、受信端のパラレル接続の端子整合技術、テオビン端子整合技術、交流端子整合技術、ダイオード端子整合技術などが含まれる。高性能信号駆動技術の応用は、端子整合技術に高い要求を突きつける。例えば、LVDS(低電圧差動信号)デバイスは、差動信号線対ミート単線インピーダンス整合だけでなく、ミート間差動インピーダンス整合も必要とする。

単一線路インピーダンスの整合より重要である。

端子整合モード及び部品の値は、回路 基板チップの駆動能力及び電力消費に関連して考慮すべきである。例えば、受信端から接地までプルダウンされた抵抗値の値は、出力電流と電圧(IOH、VOH)の値を考慮しなければならない。別の例では、ネットワーク上の信号のデューティサイクルが50 %より大きい場合、整合抵抗器は電源にプルアップされ、ネットワーク上の信号のデューティサイクルが50 %以下であるとき、整合抵抗器は接地にプルダウンされるべきである。

マッチングコンポーネントの位置の規則に関して、ソース端整合装置は、ドライバに可能な限り近くなければならないエンドマッチング装置は、受信端に可能な限り近くなければならない。ネットワークがデイジーチェーンでないならば、マッチングコンポーネントの位置とマッチング値はシリコンツールによって分析されて、決定されるべきです。

Cadenceの透視クエストは高速度システムの信号完全性解析と波形シミュレーションのための高速システム設計において指導的意義を持っている。PCB設計技術者は、回路基板のプリレイアウトを用いてシステム特性をシミュレーションすることができ、その結果、配線が完了した後、シミュレーション結果が悪いレイアウトはシミュレーション結果が悪いことが分かった。レイアウトを調整し、配線を完了した後、再びシミュレートし、貧しいネットワークの理由を分析し、良好な配線結果が得られるまで、ターゲットの改善を行う。

透視 探求のシミュレーション結果と高速システムにおけるリンギングおよび伝送線効果の実験を用いて、以下の結論を得ることができます。

プリント配線板高速信号と厳しいエッジ要件によるトレースのために、短い痕跡はできるだけ取られなければなりません。

高容量キャパシタンスを有する負荷については、短いトレース及び厚いトレースを使用すべきである。理論的解析によると、より厚いトレースはインダクタンスが小さい。

2インチより長いトレースおよび8インチより短いトレースのために、25〜50オームの減衰抵抗器は、直列に、一般に25オームまたは33オームで接続されなければならない。

8インチより長いトレースでは、並列マッチングネットワーク(グランドマッチング、パワーマッチング、中点電位マッチング、交流マッチング等)を追加すべきである。