現代, CMOS技術は、FPGAデバイスに複数のI/インタフェース. 同時に, 近年, 低消費電力が高速化の主流となっている/インタフェース. 電力消費を減らす最も効果的な方法は、電圧を下げることである, そして、電圧低下は、Iによって、許可されるより小さいノイズマージンをもたらす/インターフェイス. したがって, FPGAユーザはチップ中のシステムレベル同期スイッチングノイズ(SSN)を量子化する必要があり、パッケージ, およびPCB環境.

本論文では,ssnについて,fpga出力バッファリングによるssnを中心に系統的に紹介する。この種のノイズは一般に同期スイッチング出力ノイズ(SSO)と呼ばれ、入力バッファリングによるSSNとは異なる。システムレベルssoの原因を紹介し,層状システムレベルssoモデリング手法を提案した。同時に,ssoモデルを周波数領域と時間領域測定と関連付ける方法を説明し,ssoを低減するためのいくつかのpcb設計法を与えた。

システムレベルSSOの形成メカニズム

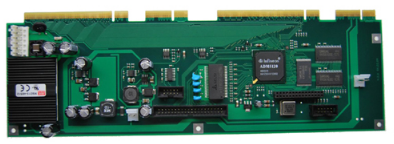

FPGAによるPCBは、能動回路を含むチップ部品に分割できる複雑なシステムである, 受動部品を埋め込んだパッケージ部品, FPGAと外部との接続を提供する回路基板部品. この種のシステムで, チップ内部の雑音特性を理解することは困難である. したがって, それは、SOの近くと遠端でSSOを定量化するのに非常に価値があります PCBトレース FPGAに接続. SSOをもたらす主な要因は、配電網(PDN)のインピーダンスとスイッチI/O間の相互誘導結合の2つである。

システムの観点から、PDNは、ウエハレベル、パッケージレベル、およびボードレベルの構成要素を含み、これらは、CMOS回路のために電力を供給する。ある数のCMOS出力駆動回路が同時にオンになると、PDNの誘導回路素子に瞬時に大きな電流が流れ、デルタ電圧降下が生じる。相互接続構成は、PCBのボール・グリッド・アレー・パッケージおよび電源ビア上のパワー・ハンダ・ボールのような寄生インダクタンスを生じる。この急速に変化する電流は、パワー/グランドプレーン対間の放射電磁波を励起する。電磁波は、PCBの平面エッジから反射され、電源/グランドプレーン間の共振を引き起こし、電圧変動を引き起こす。

ssoのもう一つの重要な原因は,相互インダクタンス結合,特にチップパッケージ/pcb端部の相互インダクタンス結合である。チップBGAパッケージ上のハンダボールおよびPCB上のビアは、密に結合されたマルチワイヤ構造に属する。各々のI / Oハンダ・ボールおよびその対応するPCBビアおよびその最寄りのハンダ・ボールおよびグランドは、閉ループを形成する。複数のI/Oポートの状態が同時に変化すると、過渡的I/O電流がこれらの信号ループを流れる。この過渡的I/O電流は、隣接する信号ループに侵入し、誘導電圧ノイズを引き起こす時変磁場を発生する。

SSOモデルはSSOの基本的な形成メカニズムを反映できる. PCB中のSSO予測のための層状モデル. チップレベルで, 我々が必要とするものは、限られた複雑さで電力線と信号線に正確な電流分布を提供することができる出力バッファモデルです. 包装レベルで, 簡単に, モデリングツールは、PDNモデルと信号結合モデルを得るのに使用できます, しかし、PDNと信号結合モデルの間の相互作用は慎重に考慮すべきである. これら2つのモデルはブリッジとして機能する, チップパッケージのバンプ端における出力バッファモデルとはんだボール端におけるPCBレベルモデルの接続. PCBのPDNモデルは、通常、電源/グランドプレーンと大容量/コンデンサのデカップリング, の間の信号結合モデル PCB 異なる信号層上の密結合ビアアレイと疎結合信号トレース. これら2つのPCBレベルモデルの相互作用効果は、PCBを介してPCBに現れる. ここから、誘導性クロストークが雑音をPDNモデルにもたらす, そして、Delta - i雑音は、ターンIの品質を減らします/シグナル. この階層的モデリング法はシミュレーション精度を合理的に維持する, 同時に、そのような複雑系の計算効率を改善する.