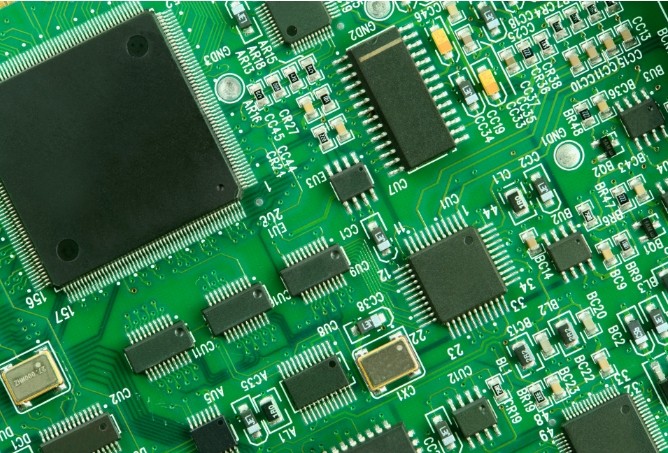

現在、表面実装素子を使用する回路基板が増えている。従来のパッケージと比較すると、回路基板の面積を減らし、バッチ加工を容易にすることができ、

また、高い配線密度を有する。SMT抵抗器とコンデンサのリードインダクタンスは大幅に低下し、これは高周波回路において大きな優位性を持っている。

表面実装アセンブリの不便な点は、手動溶接が容易ではないことです。

表面貼付アセンブリは、その形状と包装方法に応じて次のように分類されます。

1.チップ(略称C):サイズは一般的に長さ2 mm、幅1.25 mm、厚さ0.25 mmから1.5 mmの間である。

一般的なコンポーネントには、抵抗器、コンデンサ、インダクタなどがあります。

2.正方無リード(QFN):集積回路によく用いられ、異なるサイズと低インダクタンス、低抵抗の特性を有し、

3.ボールグリッドアレイ(BGA):パッケージはQFNより小さく、下には高密度回路基板設計のための多数の溶接ボールが分布している、

4.トランジスタ外形(TO):PCBに固定されたトランジスタを実装することによって保持されているが、その加工とパッケージプロセスは従来のトランジスタとは異なる、

5.小型トランジスタ(SOT):PCBにも実装により固定された小型トランジスタである。

溶接方法

1)はんだ付け前に、はんだ付け不良や酸化を避けるために、はんだ付けパッドにはんだを塗布し、はんだごてで処理することにより、はんだ付けが困難になる可能性がある。

一般的に、切りくずは処理する必要はありません。

2)ピンセットでピンを壊さないように注意してPQFPチップをPCBボードに置く。パッドに位置合わせし、配置を確実にする

チップの方向は正しい。こての温度を300℃以上に調整し、こての先端に少量の半田を塗布し、

ツールを使用して整列されたチップを下に押し、2つのアライメントピンに少量の半田を追加し、依然としてチップを下に押し、2つのアライメントピンを半田付けし、その後チップを固定する

その場で動かない。対角線を溶接した後、切り屑の位置が揃っているかどうかを再確認します。必要に応じて、調整または除去し、PCBボード上で位置合わせを行うことができます。

3)すべてのピンの溶接を開始する場合、はんだをはんだごての先端に追加し、はんだですべてのピンを塗布して湿潤を維持しなければならない。

チップ上の各ピンの端にはんだがピンに流れ込むのが見えるまではんだヘッドをタッチします。半田付けの際には、アイロンヘッドを平行に保つ必要がある

過剰溶接によるオーバーラップを防止するために。

4)すべてのピンを溶接した後、すべてのピンをはんだで濡らしてはんだを洗浄する。必要に応じて余分な半田を除去して、ショートやオーバーラップを解消します。

最後に、ピンセットで溶接点があるかどうかをチェックします。検査が完了したら、回路基板上の半田を除去し、硬いブラシをアルコールに浸漬し、

半田がなくなるまで、ピンの方向に沿って丁寧に拭き取ります。

5)SMT抵抗素子と容量素子は比較的溶接が容易である。まず溶接点を溶接してから、部品の端を置いてピンセットで挟むことができます。

端を溶接し、正しく配置されているかどうかを確認します。位置合わせが完了している場合は、もう一方の端を溶接します。本当に溶接技術を身につけるには、大量の練習が必要だ。

表面実装部品は電子製造において重要な役割を果たし、その品質は製品の性能と信頼性に直接影響を与える。

同時に、従来のプラグインアセンブリに比べて、表面実装アセンブリは製造と実装の過程でより便利で効率的であり、

生産性を大幅に向上させ、コストを削減することができます。