Hoy en día, la tecnología CMOS permite que los dispositivos FPGAs tengan múltiples interfaces de E / S. Al mismo tiempo, en los últimos años, el bajo consumo de energía ha comenzado a convertirse en el concepto principal de la interfaz de E / s de alta velocidad. La forma más eficaz de reducir el consumo de energía es reducir el voltaje, que hará que la interfaz de E / s permita una menor tolerancia al ruido. Por lo tanto, es muy necesario para los usuarios de FPGAs cuantificar el ruido de conmutación síncrona a nivel de sistema (ssn) en entornos de chip, encapsulamiento y pcb.

Este artículo presenta sistemáticamente ssn, centrándose en SSN causado por el amortiguación de salida de fpgas. Este ruido se conoce comúnmente como ruido de salida del interruptor sincronizado (sso), que es diferente del SSN causado por el amortiguador de entrada. Este artículo presenta las causas de la generación de SSO a nivel de sistema y propone un método jerárquico de modelado de SSO a nivel de sistema. Al mismo tiempo, este artículo también explica cómo asociar el modelo SSO con mediciones de frecuencia y dominio de tiempo, y da varios métodos de diseño de PCB para reducir sso.

El mecanismo de formación de SSO a nivel de sistema

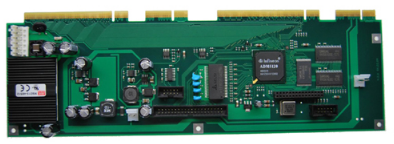

El PCB con FPGAs es un sistema complejo que se puede dividir en una parte del CHIP que contiene un circuito activo, una parte encapsulada de un componente pasivo integrado con un rastro de soporte y una parte de la placa de circuito que proporciona una conexión de FPGAs con el exterior. En este tipo de sistema, es difícil entender las características de ruido dentro del chip. Por lo tanto, es muy valioso cuantificar los SSO cercanos y remotos de los rastros de PCB conectados a la fpgas. Hay dos factores principales que conducen al sso: el acoplamiento de inducción mutua entre la resistencia de la red de distribución (pdn) y el I / o del interruptor.

Desde el punto de vista del sistema, el pdn incluye componentes a nivel de chip, nivel de encapsulamiento y nivel de placa, que juntos proporcionan energía a los circuitos cmos. Cuando un cierto número de circuitos de accionamiento de salida CMOS se conducen simultáneamente, la gran corriente fluirá instantáneamente a los componentes del Circuito de inducción de pdn, lo que provocará una caída de tensión delta - I. La estructura de interconexión produce inductores parasitarios, como bolas de soldadura de potencia en envases de matriz de rejilla de bola y agujeros de potencia en pcb. Esta corriente que cambia rápidamente también estimula ondas electromagnéticas radiales entre pares de planos de potencia / tierra. Las ondas electromagnéticas se reflejan desde el borde plano del pcb, generando resonancia entre el plano de alimentación / tierra y provocando fluctuaciones de voltaje.

Otra razón importante de SSO es el acoplamiento de inducción mutua, especialmente alrededor del borde del encapsulamiento del chip / pcb. La bola de soldadura en el paquete bga del CHIP y el agujero en el PCB pertenecen a una estructura multilínea estrechamente acoplada. Cada bola de soldadura I / o y sus correspondientes agujeros de paso de PCB y sus bolas de soldadura de tierra más cercanas y agujeros de paso de tierra forman un circuito cerrado. Cuando el Estado de varios puertos de E / s cambia simultáneamente, la corriente instantánea de E / s fluye a través de estos circuitos de señal. Esta corriente instantánea de E / s producirá un campo magnético variable en el tiempo que invade los circuitos de señal adyacentes y causa ruido de voltaje inducido.

Un excelente modelo de SSO debería ser capaz de reflejar el mecanismo básico de formación de sso. Modelo jerárquico utilizado para predecir SSO en pcb. A nivel de chip, lo que necesitamos es un modelo de amortiguación de salida que pueda proporcionar una distribución precisa de la corriente en líneas de alimentación y señal con complejidad limitada. A nivel de encapsulamiento, por simplicidad, se pueden utilizar herramientas de modelado para obtener modelos pdn y modelos de acoplamiento de señales, pero se debe considerar cuidadosamente la interacción entre pdn y modos de acoplamiento de señales. Estos dos modelos actúan como puentes, conectando el modelo de amortiguación de salida del extremo del punzón del paquete del CHIP y el modelo de nivel PCB del extremo de la bola de soldadura. Los modelos pdn de los PCB suelen incluir el plano de alimentación / tierra y los condensadores de gran capacidad / desacoplamiento en él, mientras que los modelos de acoplamiento de señal de los PCB incluyen una matriz de agujeros de acoplamiento apretado y trazas de señal de acoplamiento suelto en diferentes capas de señal. Los efectos interactivos de estos dos modelos a nivel de PCB aparecen en los PCB a través de la matriz. Es desde aquí donde la conversación cruzada inductiva lleva el ruido al modelo pdn, y el ruido delta - I a su vez reduce la calidad de la señal de E / S. Este método de modelado jerárquico mantiene razonablemente la precisión de la simulación y, al mismo tiempo, mejora la eficiencia informática de tales sistemas complejos.