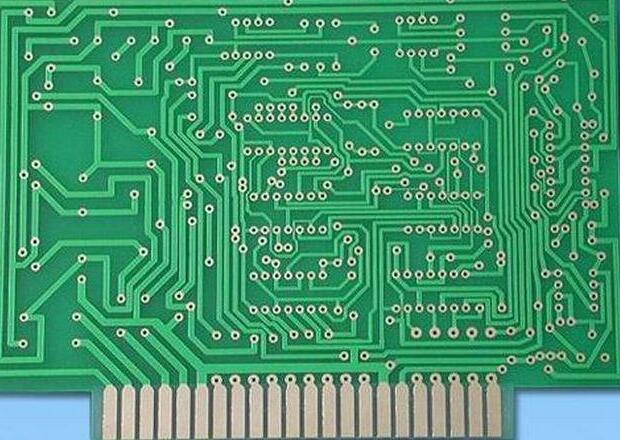

Why do we need to do serpentine isometric design in PCB design

In PCB design, equal-length traces are mainly for some high-speed parallel buses.

Since this type of parallel bus often has multiple data signals sampled based on the same clock, each clock cycle may need to be sampled twice (DDRSDRAM) or even 4 times. As the operating frequency of the chip increases, the signal transmission delay affects the timing The proportion is getting larger and larger. In order to ensure that the value of all signals can be collected correctly at the data sampling point (the rising or falling edge of the clock), the delay of signal transmission must be controlled. The purpose of equal-length traces is to minimize the difference in transmission delay of all relevant signals on the PCB.

The effective establishment and maintenance window of high-speed signals is relatively small. To make data and control signals fall within the effective window, the difference in trace length between data, clock or data, and between control signals is very small. The specific allowable deviation can be obtained by calculating the time delay.

In fact, in general, sequential logic signals must meet the setup time and hold time and have a certain margin. As long as this condition is met, the signal may not be strictly equal in length.

However, the actual situation is that for high-speed signals (such as DDR2, DDR3, FSB), it is impossible to know whether the timing meets the setup time and hold time requirements during the design (there are too many influencing factors, including the internal wiring and capacitance of the chip). The delay difference caused by the load must be considered, it is difficult to estimate the actual value through calculation), a controllable delay device must be set inside the chip (the delay is controlled by the register), and then the value of the register is scanned to try various delays. And by observing the signal (look at the waveform directly, and measure the setup and hold time) to determine the delay value to meet the setup time and hold time requirements. However, the same type of signal is generally only observed for one or a few of the signal lines. In order to make all the signals meet the timing requirements, the same type of signal wiring must be strictly equal in length.

We are not an agent

Our factory is located in China. For decades, Shenzhen has been known as the world's electronics R&D and manufacturing center. Our factory and website are approved by the Chinese government, so you can skip the middlemen and buy products on our website with confidence. Because we are a direct factory, this is the reason why 100% of our old customers continue to purchase on iPCB.

No minimum requirements

You can order as little as 1 PCB from us. We will not force you to buy things you really don't need to save money.

Free DFM

Before you pay in the most timely manner, all your orders will receive free engineering document review services by our well-trained professional and technical personnel.