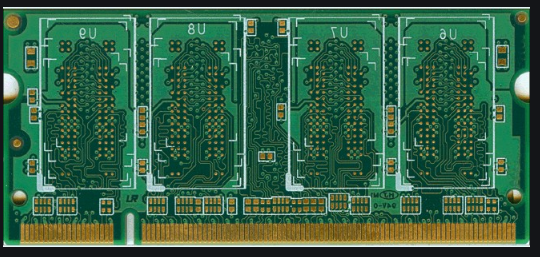

Ниже описаны два основных метода проектирования, основанных на механизме генерации SSO на печатных платах с FPGA для уменьшения SSO.

Методы проектирования для уменьшения индуктивной связи

Результаты моделирования показывают, что индуктивная связь на интерфейсе инкапсуляции чипа / PCB является виновником высокочастотных пиков в форме волны SSO. Сигнальная петля размером t * d состоит из сигнальных перфораций и ближайших заземленных перфораций. Размер контура указывает на интенсивность индуктивной связи. Чем больше площадь интерференционного кольца I / O, тем легче создаваемое магнитное поле вторгается в соседнее интерференционное кольцо. Чем больше площадь нарушенного сигнального кольца ввода / вывода, тем больше он подвержен помехам со стороны других циклов ввода / вывода. Таким образом, чтобы уменьшить количество последовательных помех и параметр t, в конструкции следует использовать более тонкий PCB, а ключевые I / O на PCB должны выводиться из более мелкого сигнального слоя. В то же время проектировщики могут уменьшить помехи, сократив расстояние между перфорацией I / O и заземленным перфорацией. Дизайнеры специально соединяют пару сварных дисков I / O с плоскостью заземления и плоскостью VCCIO, чтобы уменьшить площадь сигнального кольца интерференционных и интерференционных выводов.

Для оценки эффективности метода были проведены два измерения на FPGA I / O Bank1 и Bank2. Все порты ввода / вывода в обеих группах имеют интерфейс LVTTL 2.5V с напряжением тока 12 мА и соединены с конденсатором 10pF через 50 - островную полосу.

В Bank1, AF30 является нарушенным выводом. В FPGA шесть выводов W24, W29, AC25, AC32, AE31 и AH31 запрограммированы как логические « 0» и подключены к плоскости заземления PCB через отверстие. Пять выводов U28, AA24, AA26, AE28 и AE30 запрограммированы на логический « 1» и подключены к плоскости VCCIO PCB. Другие 68 портов ввода / вывода изменяются одновременно с частотой 10 МГц, поэтому они являются источниками помех. Для сравнения, I / O W24, W29, AC25, AC32, AE31, AH31, U28, AA24, AA26, AE28 и AE30 не запрограммированы на заземление или вывод VCCIO в Bank2, но они не используются. Остальные 68 I / O остаются открытыми и закрытыми одновременно.

Экспериментальные испытания показали, что по сравнению с G30 в колонке 2 AF30 в колонке 1 подпрыгивает на 17% меньше, а временное снижение мощности - на 13%. Результаты моделирования также подтверждают это улучшение. Поскольку появление программируемых заземленных выводов сокращает расстояние между контуром помех и контуром помех d, можно ожидать уменьшения SSO. Однако, поскольку площадь сигнального кольца в упаковке чипа не может быть уменьшена, степень улучшения также ограничена.

Снижение сопротивления PDN с помощью разумной конструкции

Сопротивление между заземленными выводами интерфейса VCCIO и PCB является наиболее важным критерием для оценки производительности PDN чипа FPGA. Это входное сопротивление может быть уменьшено за счет использования эффективной стратегии развязки и использования более тонкой пары плоскости питания / заземления. Но наиболее эффективным способом является сокращение длины перепада питания, соединяющего сварочный шар VCCIO с плоскостью VCCIO. Кроме того, сокращение перфорации источника питания также уменьшит кольцевое кольцо, образованное перфорацией его и соседнего заземления, что делает кольцевое кольцо менее уязвимым для изменения состояния кольца ввода / вывода помех. Поэтому в процессе проектирования плоскость VCCIO должна быть расположена ближе к верхнему слою PCB.

Резюме

В этой статье используется FPGA для всестороннего моделирования шума синхронного переключателя на PCB. Анализ показывает, что последовательные помехи на интерфейсах инкапсуляции и PCB и распределение сопротивлений PDN на упаковке и PCB являются двумя важными причинами SSO.

Соответствующая модель может быть использована, чтобы помочь разработчикам PCB сократить SSO и улучшить дизайн PCB. В статье также описаны несколько способов сокращения SSO. Рациональное распределение сигнального слоя и полное использование программируемого заземления / вывода питания помогают снизить индуктивные помехи уровня PCB, а размещение VCCIO в более мелких местах в стеке PCB также снижает сопротивление PDN.