Whether performing ac-DC conversion or DC-DC conversion, switching power supply layouts are common in high-voltage designs and must be carefully constructed. Although the system is very common, it is prone to EMI radiation due to the rapid changes in voltage and current during switching. Designers are rarely able to apply existing designs to new systems because small changes in one area can create EMI problems that are difficult to diagnose.

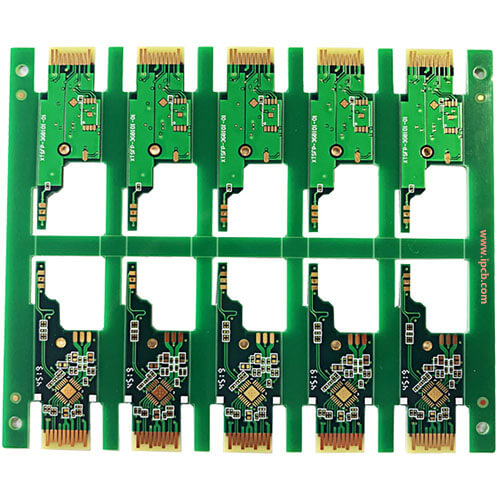

With proper PCB layout selection and wiring, noise can be prevented from becoming a major problem on the SMPS output. Low voltage converters can be purchased as ics with different shape factors, but high voltage converters will need to be manufactured from discrete components on dedicated boards. Here are some important SMPSPCB layout tips to help you keep components cool and prevent noise problems in your system.

Noise and Heat problems in SMPS PCB layout

There is no solution: any SMPS will produce moderate high-frequency noise due to the switching action of the transistor driver. In effect, you are converting low-frequency ripple (that is, generated from a full-wave rectifier during ac-DC conversion) to high-frequency switching noise. Although this conversion produces a more stable DC output, there are still two important sources of noise:

Direct switching noise from switching elements.

Transient noise elsewhere in the system.

Noise will appear on the output of SMPS unit in the form of conduction noise and radiation noise. Although the cause of each problem is difficult to diagnose, two types of noise can be easily distinguished. Other design challenges in the SMPSPCB layout are the heat generated on the board. While this can be influenced by choosing the right PWM frequency, duty cycle, and rise time, you still need to use the right thermal management strategy on the board. With these two challenges in mind, let's take a look at some of the details to note in the LAYOUT of SMPSPCB.

Thermal management

Ideally SMPS will dissipate zero power, although this does not actually happen. Your switching transistor (and the input transformer for the AC-DC conversion) will dissipate most of the heat. Even when the efficiency can reach 90% in a switching power supply topology, power MOSFEts can still emit a lot of heat during switching. A common practice here is to place the radiator on the key switch assembly. Be sure to reconnect them to the ground formation to prevent new EMI.

In high voltage/high current power supplies, these radiators can be quite large. You can install fans in the chassis to enhance the heat dissipation capability of the system. Also, be sure to follow good practices for powering the fan to prevent new EMI problems.

Some SMPSPCB layout tips

Your stack

Your layout will help with thermal management to some extent, but this is a bigger determinant of EMI sensitivity. In general, conducted noise is dealt with by using EMI filters on input and output circuits. Like many EMI issues in high speed/high frequency systems, your stack will be a major determinant of resistance to radiated EMI.

The correlation frequency range of SMPS operation is? 10 KHZ to? 1MHz, so the radiated EMI will sense the induced noise. Therefore, you want to place the grounding layer directly under the surface layer with all the power components. This will ensure low loop inductance for the surface circuit. Any induced noise signal propagated to the output is normally eliminated by filtering at the output.

The transient ringing

Transients are a harder problem to solve because they are related to your lamination, wiring, presence of holes, and excessive decoupling/impedance. As is the case in high-speed design, do not route any copper carrying a switch signal into the ground gap, as this will form a certain type of antenna structure that will radiate strongly during transients. These transients tend to be high frequency (anywhere from 10 to 100 MHZ).

The problem of transient ringing is an impedance management problem. High impedance results in strong voltage ripple. The components shall be placed with the correct pad pattern to reduce the impedance in the PDN of the board.