(1) cabaran yang dihadapi oleh desain sistem elektronik

Dengan peningkatan skala besar dalam kompleksiti desain sistem dan integrasi, perancang sistem elektronik terlibat dalam desain sirkuit di atas 100MHZ, dan frekuensi operasi bas telah mencapai atau melebihi 50MHZ, dan beberapa bahkan melebihi 100MHZ. Pada masa ini, sekitar 50% rancangan mempunyai frekuensi jam lebih dari 50MHz, dan hampir 20% rancangan mempunyai frekuensi jam lebih dari 120MHz.

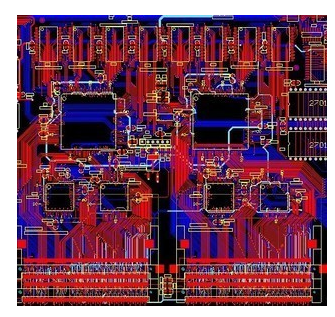

Apabila sistem berfungsi pada 50MHz, akan ada kesan garis penghantaran dan masalah integriti isyarat; apabila jam sistem mencapai 120MHz, kecuali pengetahuan rancangan sirkuit kelajuan tinggi digunakan, PCB direka berdasarkan kaedah tradisional tidak akan berfungsi. Oleh itu, teknologi rancangan PCB kelajuan tinggi telah menjadi kaedah rancangan yang perancang sistem elektronik mesti menerima. Kemudahan kawalan proses desain hanya boleh dicapai dengan menggunakan teknik desain pereka sirkuit kelajuan tinggi.

(2) Apakah sirkuit kelajuan tinggi

Secara umum dipercayai bahawa jika frekuensi sirkuit logik digital mencapai atau melebihi 45MHZ~50MHZ, dan sirkuit yang bekerja di atas frekuensi ini telah mengambil bahagian tertentu dari seluruh sistem elektronik (misalnya, 1/3), ia dipanggil sirkuit kelajuan tinggi.

Sebenarnya, frekuensi harmonik pinggir isyarat lebih tinggi daripada frekuensi isyarat sendiri. Ia adalah pinggir yang meningkat dan jatuh isyarat (atau lompat isyarat) yang menyebabkan hasil tidak dijangka dalam penghantaran isyarat. Oleh itu, secara umum disetujui bahawa jika lambat penyebaran garis lebih besar daripada 1/2 masa naik hujung pemandu isyarat digital, isyarat tersebut dianggap sebagai isyarat kelajuan tinggi dan menghasilkan kesan garis pemandu.

Pemindahan isyarat berlaku pada saat keadaan isyarat berubah, seperti masa naik atau jatuh. isyarat melepasi masa yang tetap dari hujung pemandu ke hujung penerimaan. Jika masa penghantaran kurang dari 1/2 masa naik atau jatuh, isyarat terrefleks dari hujung penerima akan mencapai hujung pemandu sebelum isyarat mengubah keadaan. Sebaliknya, isyarat terreflected akan mencapai akhir pemacu selepas isyarat mengubah keadaan. Jika isyarat terrefleksi kuat, bentuk gelombang yang tergantung mungkin mengubah keadaan logik.

(3) Penentuan isyarat kelajuan tinggi

Di atas kita telah menentukan persyaratan untuk kejadian kesan garis transmisi, tetapi bagaimana kita tahu sama ada lambat garis lebih besar daripada 1/2 masa naik isyarat hujung pemacu? Secara umum, nilai biasa masa naik isyarat boleh diberi dalam manual peranti, dan masa penyebaran isyarat ditentukan oleh panjang kawat sebenar dalam reka PCB. Korespondensi antara masa naik isyarat dan panjang kawat yang boleh dibenarkan (lambat).

Lembatan per unit inci pada PCB adalah 0.167ns. Namun, jika terdapat banyak vias, banyak pins peranti, dan banyak kekangan ditetapkan pada kabel rangkaian, kelalaian akan meningkat. Secara umum, masa naik isyarat peranti logik kelajuan tinggi adalah kira-kira 0.2ns. Jika ada cip GaAs di papan, panjang kabel maksimum adalah 7.62mm.

Biarkan Tr adalah masa naik isyarat dan Tpd adalah lambat penyebaran garis isyarat. Jika Tr â¥4Tpd, isyarat jatuh di kawasan yang selamat. Jika 2Tpdâ¥Trâ¥4Tpd, isyarat jatuh dalam kawasan ketidakpastian. Jika Tr ⤤2Tpd, isyarat jatuh di kawasan masalah. Untuk isyarat jatuh di kawasan tidak pasti dan kawasan masalah, kaedah kabel PCB kelajuan tinggi patut digunakan.