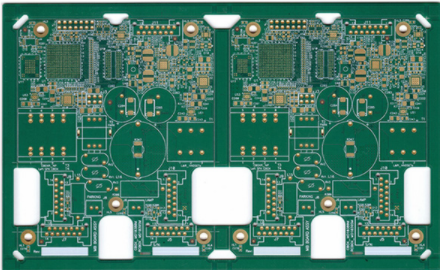

Rancangan papan sirkuit adalah tugas yang memakan masa dan memakan masa. Setiap masalah memerlukan jurutera untuk memeriksa keseluruhan rancangan pada dasar komponen demi komponen. Ia boleh dikatakan bahawa keperluan desain papan sirkuit adalah sebaik desain cip.

Proses reka PCB biasa termasuk langkah berikut:

Tiga langkah pertama mengambil masa yang paling lama kerana pemeriksaan skematik adalah proses manual. Bayangkan papan SoC dengan 1000 atau lebih sambungan. Memeriksa setiap sambungan secara manual adalah tugas yang membosankan. Sebenarnya, hampir mustahil untuk memeriksa setiap sambungan, yang mungkin menyebabkan masalah di papan akhir, seperti sambungan yang salah, nod mengapung, dll.

Tahap penangkapan skematik biasanya menghadapi jenis masalah berikut:

Ralat skor bawah: contohnya, APLLVDD dan APLL_VDD

Soalan kes: seperti VDDE dan vdde

Ralat ejaan

Masalah sirkuit pendek isyarat

Ada lagi......

Untuk menghindari ralat ini, sepatutnya ada cara untuk memeriksa skema lengkap dalam beberapa saat. Kaedah ini boleh diselesaikan dengan simulasi diagram skematik, yang jarang dalam proses reka papan sirkuit semasa. Simulasi skematik membolehkan anda melihat output akhir pada nod yang diinginkan, jadi ia secara automatik memeriksa untuk semua isu sambungan.

Berikut dijelaskan oleh contoh projek. Anggap diagram blok papan sirkuit biasa:

Bagaimana untuk mengurangi ralat desain PCB dan meningkatkan efisiensi desain anda dalam bentangan PCB

Dalam rancangan papan sirkuit kompleks, boleh ada ribuan sambungan digital, dan sedikit perubahan mungkin membuang banyak masa untuk pemeriksaan.

Simulasi skematik tidak hanya boleh simpan masa desain, tetapi juga meningkatkan kualiti papan sirkuit dan meningkatkan keseluruhan efisiensi proses.

DUT biasa mempunyai isyarat berikut:

Selepas beberapa pra-penyesuaian, peranti yang sedang diuji akan mempunyai pelbagai isyarat dan pelbagai modul untuk penyesuaian isyarat, seperti pengatur tegangan, penyembah operasi, dan sebagainya. Anggap contoh isyarat kuasa yang diperoleh oleh pengatur tegangan:

Untuk mengesahkan sambungan dan melakukan pemeriksaan keseluruhan, simulasi skematik digunakan. Simulasi skematik termasuk penciptaan skematik, penciptaan platform ujian dan simulasi.

Semasa mencipta platform ujian, isyarat stimulus dihantar ke input yang diperlukan, dan kemudian output diawasi pada titik isyarat yang menarik.

Proses di atas boleh diselesaikan dengan menyambung sonda ke nod yang hendak dilihat. Tengah nod dan bentuk gelombang boleh menunjukkan sama ada ada ralat dalam skema. Semua sambungan isyarat semak secara automatik.

Bagaimana membiarkan penghasil PCB mengurangi ralat dalam rancangan PCB dan meningkatkan efisiensi rancangan mereka

Mari kita lihat, nod dan tekanan yang terdeteksi jelas terlihat:

Dengan bantuan simulasi, kita boleh terus mengamati keputusan dan mengesahkan bahawa diagram skematik papan PCB adalah betul. Selain itu, mungkin untuk menyelidiki perubahan rancangan dengan menyesuaikan dengan hati-hati isyarat stimulus atau nilai komponen. Oleh itu, simulasi skematik boleh menyimpan banyak masa untuk reka papan sirkuit dan staf pemeriksaan, dan meningkatkan kemungkinan keperluan reka.