System level packaging (SIP) is no longer a simple packaging technology, and these technologies include PoP, CoC, WLP, TSV, Embedded Substrate, etc. It also involves the development of other packaging processes such as wire bonding, flip chip, micro bumps, etc.

Stacked Package (PoP)

Stacked encapsulation (PoP) can provide more functionality in a smaller space. Stacked packaging can be used to develop multi chip packages with different functions, or to place multiple storage chips in a package with increased capacity. System level encapsulation (SiP) can implement various system components in a single package. These technologies enable semiconductor companies to create high value-added products while also meeting the diverse demands of the market.

Package stacking is the process of vertically stacking packages. Packet to packet stacking (PoP) is the most commonly used stacking method and has been widely used in mobile devices. For PoP in mobile devices, the types and functions of chips used in the upper and lower packaging may vary, and chip manufacturers may also be different.

The common PoP, the upper packaging mainly includes storage chips produced by semiconductor storage companies, while the stacked packaging below mainly includes chips with mobile processors. Due to packaging being produced by different manufacturers, quality inspection is required before stacking. Even if defects occur after stacking, defective components can be replaced with new packaging for rework.

Chip on Chip(CoC)

COC packaging process is a commonly used integrated circuit packaging technology, which is widely used in the field of electronic product manufacturing. COC (Chip on Chip) is a technology that encapsulates multiple chips in the same package. By stacking multiple chips together, it can effectively improve the integration of circuits, reduce the size of circuit boards, and improve the performance and reliability of circuits.

In the COC packaging process, the first step is to select and test the chips. Chip selection refers to selecting chips that meet the requirements from a large batch of chips, which requires strict testing and screening to ensure the quality and performance of the chips. Then, multiple chips are stacked together using precise positioning and stacking techniques to form a whole. During the stacking process, precise positioning devices and adhesives are required to ensure the accurate positioning of the chips and maintain stability during the packaging process.

The key to COC packaging technology lies in the connection of chips. After stacking, it is necessary to electrically connect the chips to achieve data transmission and communication between them. This is usually achieved through micro soldering or cable connections. Micro soldering is the use of tiny solder joints to connect the pins between chips, while cable connection is the use of small metal wires to connect the pins between chips. These connections require precise operation and high technical requirements to ensure their reliability and stability.

After the packaging is completed, it is necessary to perform appearance treatment and testing. Appearance treatment refers to the beautification and protection of the packaging body to improve the appearance and quality of the product. This process includes coating, polishing, and polishing of the packaging body, as well as labeling and packaging completion. Testing refers to conducting electrical performance and reliability tests on packaged chips to ensure that they meet design requirements and can function properly.

The application of COC packaging technology is very extensive. It can be used for packaging various integrated circuits, including microprocessors, memory, communication chips, etc. The COC packaging process can improve the integration and performance of circuits, reduce the size of circuit boards, lower system power consumption, and enhance system reliability and stability. Therefore, it is widely used in the manufacturing of electronic products such as mobile phones, tablets, televisions, and cameras.

COC packaging process is a technology that encapsulates multiple chips in the same package. It achieves circuit integration, miniaturization, and high performance through processes such as chip selection, stacking, and connection, as well as appearance processing and testing. The COC packaging process plays an important role in electronic product manufacturing, as it not only improves the performance and reliability of circuits, but also reduces the size and power consumption of products.

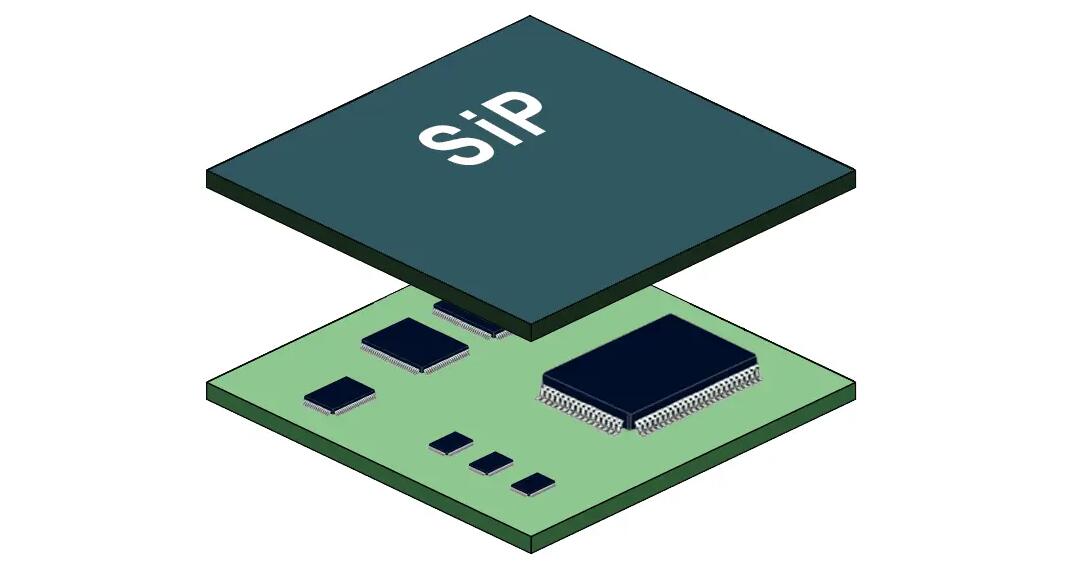

System level packaging (SIP)

The advantages of system level packaging (SIP)

1. High packaging efficiency, SiP packaging technology adds multiple chips within the same package, greatly reducing packaging volume and improving packaging efficiency.

2. The product has a short launch cycle, and due to SIP packaging being different from SOC, it does not require layout and routing at the layout level, reducing the complexity of design, verification, and debugging and shortening the system implementation time. Even if partial design changes are required, it is much simpler and easier than Soc.

3. Good compatibility, SIP packaging combines chips made of different processes and materials into a system that can achieve a dream combination of embedded integrated passive components. Passive components currently used in wireless and portable electronic devices can be embedded with at least 30-50% λ.

4. Reducing system costs, SIP can provide low-power and low-noise system level connections, and operating at higher frequencies can achieve a wider bandwidth and almost the same bus bandwidth as SOC. A dedicated integrated circuit system using SIP encapsulation technology can save more system design and production costs than SOC.

5. The physical size is small, and the thickness of SIP packaging is constantly decreasing. The most advanced technology can achieve ultra-thin packaging with only 1.0mm thickness for five layer stack chips, and reduce the weight of three-layer chip packaging by 35%.

6. High electrical performance, SIP packaging technology can combine multiple packages into one, greatly reducing the total number of solder joints, significantly reducing package volume and weight, shortening component connection routes, and thus improving electrical performance.

7. Widely used, SIP packaging is different from traditional chip packaging. It can not only handle digital systems, but also be applied in fields such as optical communication, sensors, and microelectromechanical systems (MEMS).

The main application areas of SIP encapsulation

SIP has a wide range of applications, including wireless communication, automotive electronics, medical electronics, computers, military electronics, etc. The most widely used field among them is wireless communication.

SIP was first and most widely used in the field of wireless communication. In the field of wireless communication, the requirements for functional transmission efficiency, noise, volume, weight, and cost are becoming increasingly high, forcing wireless communication to develop towards low-cost, portable, multifunctional, and high-performance directions.

SIP is an ideal solution that combines the advantages of existing core resources and semiconductor production processes, reduces costs, shortens time to market, and overcomes difficulties such as process compatibility, signal mixing, noise interference, electromagnetic interference, etc. in SOC.

SIP encapsulation technology is an advanced system integration and encapsulation technology. Compared with other encapsulation technologies, SIP technology has a series of unique technical advantages, which meet the development needs of lighter, smaller, and thinner electronic products today. It has a broad application market and development prospects in the field of microelectronics.