Sekarang ini, teknologi CMOS membolehkan peranti FPGA mempunyai antaramuka I/O berbilang. Pada masa yang sama, dalam tahun-tahun terakhir, konsumsi tenaga rendah telah mula menjadi konsep utama antaramuka kelajuan tinggi I/O. Cara paling efektif untuk mengurangi konsumsi kuasa adalah mengurangi tenaga, dan pengurangan tenaga akan menghasilkan margin bunyi yang lebih kecil yang dibenarkan oleh antaramuka I/O. Oleh itu, ia sangat diperlukan bagi pengguna FPGA untuk kuantifikasi bunyi penyukaran sinkronik aras sistem (SSN) dalam persekitaran cip, pakej, dan PCB.

Artikel ini memperkenalkan SSN secara sistematik, fokus pada SSN disebabkan oleh penimbal output FPGA. Jenis bunyi ini biasanya dipanggil Bunyi Output Penukaran Sinkron (SSO), yang berbeza dari SSN disebabkan oleh penimbal input. Artikel ini memperkenalkan penyebab SSO aras sistem, dan mencadangkan kaedah pemodelan SSO aras sistem lapisan. Pada masa yang sama, artikel ini juga menjelaskan bagaimana untuk mengaitkan model SSO dengan pengukuran domain frekuensi dan domain masa, dan memberikan beberapa kaedah reka PCB untuk mengurangkan SSO.

Mekanisme formasi SSO aras sistem

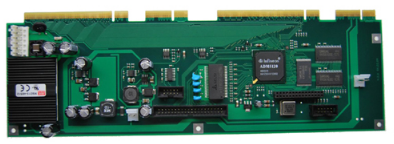

PCB dengan FPGA adalah sistem kompleks yang boleh dibahagi ke bahagian cip yang mengandungi sirkuit aktif, bahagian pakej dengan komponen pasif yang menyokong jejak, dan bahagian papan sirkuit yang menyediakan sambungan antara FPGA dan luar. Dalam jenis sistem ini, sukar untuk memahami ciri-ciri bunyi di dalam cip. Oleh itu, ia sangat berharga untuk kuantifikasi SSO pada hujung dekat dan jauh jejak PCB yang tersambung ke FPGA. Terdapat dua faktor utama yang menyebabkan SSO: pengendalian rangkaian distribusi kuasa (PDN) dan sambungan induksi antara switch I/O.

Dari perspektif sistem, PDN termasuk aras-wafer, aras-pakej, dan komponen-aras-papan, yang bersama-sama menyediakan kuasa untuk sirkuit CMOS. Apabila bilangan tertentu sirkuit pemacu output CMOS dihidupkan pada masa yang sama, arus besar akan mengalir ke dalam unsur sirkuit induktif PDN secara segera, yang mengakibatkan jatuh tegangan delta-I. Struktur sambung antara menghasilkan induksi parasit, seperti bola tentera kuasa pada pakej tata grid bola dan vias kuasa dalam PCB. Semasa yang berubah dengan cepat juga menggairahkan gelombang elektromagnetik radial antara pasangan pesawat kuasa/tanah. Gelombang elektromagnetik tersembunyi dari pinggir planar PCB, mencipta resonansi antara pesawat kuasa/tanah, dan menyebabkan perubahan tegangan.

Satu lagi penyebab penting bagi SSO adalah sambungan induktif bersama, terutama sambungan induktif bersama sekitar pinggir pakej cip/PCB. Bola solder pada pakej chip BGA dan vias pada PCB milik struktur berbilang-wayar yang terikat dengan ketat. Setiap bola tentera I/O dan PCB yang sepadan melalui dan bola tentera tanah terdekat dan tanah melalui bentuk loop tertutup. Apabila keadaan pelabuhan I/O berbilang berubah pada masa yang sama, arus I/O sementara mengalir melalui gelung isyarat ini. Semasa I/O sementara ini akan menghasilkan medan magnetik yang berbeza-masa, yang menyerang gelung isyarat sebelah dan menyebabkan bunyi tekanan.

Model SSO yang baik seharusnya dapat mencerminkan mekanisme formasi asas SSO. Model lapisan untuk meramalkan SSO dalam PCB. Pada aras cip, apa yang kita perlukan adalah model penimbal output yang boleh menyediakan distribusi semasa yang tepat pada garis kuasa dan garis isyarat dengan kompleksiti terhad. Pada aras pakej, untuk kemudahan, alat pemodelan boleh digunakan untuk mendapatkan model PDN dan model sambungan isyarat, tetapi interaksi antara PDN dan model sambungan isyarat patut dipertimbangkan dengan berhati-hati. Dua model ini bertindak sebagai jambatan, menyambung model penimbal output pada hujung bump pakej cip dan model aras PCB pada hujung bola tentera. Model PDN PCB biasanya termasuk kapasitas tenaga/tanah dan kapasitas-besar/pemisah kapasitas di atasnya, sementara model sambungan isyarat PCB termasuk secara ketat tersambung melalui tatasusunan dan jejak isyarat terlepas pada lapisan isyarat yang berbeza. Kesan interaksi dua model aras-PCB ini muncul dalam PCB melalui array. Dari sini, percakapan salib induktif membawa bunyi ke dalam model PDN, dan bunyi delta-I menurunkan kualiti isyarat I/O. Kaedah pemodelan hierarkis ini menyimpan ketepatan simulasi secara rasional, dan pada masa yang sama meningkatkan efisiensi pengiraan sistem kompleks seperti ini.