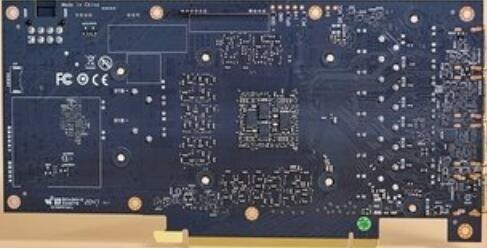

в метод проектирования PCB based on signal integrity computer analysis, создание модели целостности сигналов уровня PCB, это отличается от традиционного дизайна.

The correctness of the SI model will determine the correctness of the design, возможность построения модели си определяет осуществимость такого проектного подхода.

4.1. модель SI для PCB

There are many models that can be used for PCB board-level signal integrity analysis in electronic design. три наиболее распространенных вида пряности, IBIS и Verilog - A.

модель пряности

пряности - это сила

l general-purpose analog circuit simulator. В настоящее время модель SPICE широко используется в электронном проектировании, and two main versions have been derived: HSPICE and PSPICE. HSPICE используется главным образом для проектирования интегральных схем, while PSPICE is mainly used in PCB board and system-level design.

модель SPICE состоит из двух компонентов: уравнение модели и параметры модели. Благодаря наличию модельных уравнений модель SPICE может быть тесно увязана с алгоритмом имитатора, что позволит получить более эффективный анализ и результаты анализа.

при использовании модели SPICE уровень PCB, it is necessary for the integrated circuit designer and manufacturer to provide a detailed and accurate description of the SPICE model of the integrated circuit I/Параметры изготовления полупроводниковой схемы и полупроводниковой характеристики. Потому что эти материалы обычно принадлежат дизайнерам и изготовителям права интеллектуальной собственности и конфиденциальность, only a few semiconductor manufacturers will provide corresponding SPICE models while providing chip products.

точность анализа модели SPICE зависит главным образом от источника параметров модели (т.е. сочетание уравнений модели и различных цифровых имитаторов также может повлиять на точность анализа. Кроме того, модель SPICE класса PCB имеет множество аналоговых расчетов, и анализ занимает много времени.

B, модель ибиса

модель IBIS, первоначально Разработанная компанией « интел», используется для анализа целостности цифровых сигналов уровня PCB и системного уровня. It is now managed by the IBIS Open Forum and has become an official industry standard (EIA/ANSI 656-A).

модель IBIS использует таблицы I / V и V / T для описания характеристик элементов и элементов цифровой интегральной схемы I / O. Поскольку модель IBIS не требует описания внутренних конструкций модуля I / O и параметров изготовления транзисторов, Производители полупроводников приветствуют ее и поддерживают ее. В настоящее время все крупные производители цифровых интегральных схем могут предоставлять соответствующие модели IBIS одновременно с предоставлением чипов.

точность анализа модели IBIS зависит главным образом от количества точек данных в таблицах I / V и V / T, а также от точности данных. В результате использования контрольных таблиц для моделирования уровней PCB на основе модели IBIS расчетные показатели являются небольшими и, как правило, составляют от 1 / 10 до 1 / 100 соответствующей модели SPICE.

C. модель Verilog AMS и модель VHDL - AMS

Verilog AMS и VHDL - AMS появились менее 4 лет назад, and they are a new standard. как язык моделирования уровня аппаратных средств, Verilog-AMS and VHDL-AMS are supersets of Verilog and VHDL, по отдельности, while Verilog-A is a subset of Verilog-AMS.

В отличие от моделей SPICE и IBIS, на языке AMS пользователи готовят формулы для описания поведения компонентов. как и в случае с моделью IBIS, язык моделирования AMS является самостоятельным форматом модели, который может использоваться во многих моделях. уравнение AMS может быть также подготовлено на многих уровнях: уровне транзистора, уровне модуля I / O, блоке I / O и т.д.

Поскольку Verilog AMS и VHDL - AMS являются новыми стандартами, на сегодняшний день лишь немногие Производители полупроводников могут предложить модели AMS и менее активно поддерживают AMS, чем SPICE и IBIS. Однако эффективность и точность вычислений модели AMS в анализе полноты сигналов уровня PCB не ниже, чем модели SPICE и IBIS.

4.2 выбор типа

из - за отсутствия единой модели для завершения анализа полноты всех сигналов уровня PCB, in the design of high-speed digital PCB board, it is necessary to mix the above-mentioned models to establish the transmission model of key signals and sensitive signals to the greatest extent.

для отдельных пассивных элементов можно было бы использовать модель SPICE, предложенную изготовителем, или создать упрощенную модель SPICE непосредственно и использовать ее на экспериментальной основе.

для ключевых цифровых интегральных схем необходимо искать модели IBIS, предлагаемые изготовителем. В настоящее время большинство дизайнеров и производителей интегральных схем могут предлагать необходимые модели IBIS одновременно с предоставлением чипов через веб - сайт или иным образом.

В случае неликвидных интегральных схем, если модель IBIS производителя недоступна, можно также выбрать аналогичную или стандартную модель IBIS в соответствии с функцией фишки - пятки. Конечно, можно было бы создать упрощенную модель IBIS на основе экспериментальных измерений.

Что касается линий передачи на панелях PCB, то упрощенная модель SPICE может использоваться для предварительного анализа целостности сигналов и пространственного анализа, тогда как модель SPICE для полной линии передачи должна быть спроектирована в соответствии с реальной схемой для последующего анализа.