проектирование печатных плат является очень трудоемкой задачей.любой вопрос требует от инженера поочередно осмотреть весь проект.можно сказать,что требования конструкции платы так же хороши,как и дизайн чипа.

Процесс типичного проектирования печатных плат включает следующие этапы:

Первые три шага занимают больше всего времени, потому что проверка схемы это ручной процесс. Представьте себе блок с 1000 или более соединений. Ручная проверка каждого соединения непростая задача.На самом деле,невозможно проверить каждое соединение, это может привести к проблемам на плате, таким как неправильные соединения,плавающие узлы и т.д.

на стадии захвата схемы обычно возникают следующие типы проблем:

ошибка подчёркивания:например,APLLVDD и APLL DU VDD Тематические вопросы:например,VDDE и VDDE орфографический ошибка Проблема короткого замыкания сигнала И еще.

Чтобы избежать этих ошибок,должен существовать способ проверить всю схему в течение нескольких секунд. Этот способ может быть реализован с помощью моделирования принципиальной схемы,что редко встречается в современном процессе проектирования плат. Схема позволяет просматривать конечный вывод на нужном узле,поэтому она автоматически проверяет все проблемы с соединением.

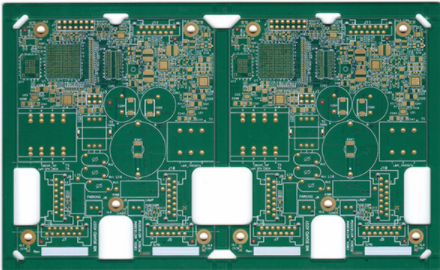

Ниже приводятся примеры проектов. рассмотрим типичную схемную схемную схему:

как уменьшить ошибки при проектировании печатных плат и повысить эффективность проектирования в схеме печатной платы

при сложном проектировании платы могут быть тысячи цифровых соединений, и незначительные изменения могут привести к потере времени на проверку.принципиальная схема моделирования может не только экономить время проектирования, но и повысить качество платы, повысить общую технологическую эффективность.

типичный DUT имеет следующие сигналы:

После некоторой предварительной корректировки измеренное оборудование будет иметь различные модули настройки сигналов и сигналов, такие, как регулятор напряжения, операционный усилитель и т.д.Пример сигнала мощности, получаемого регулятором напряжения:

Чтобы проверить соединение и провести общую проверку, схемотехническое моделирование включает в себя создание схемы, создание и моделирование тестовой платформы.

в процессе создания тестовой платформы,стимулирующие сигналы посылаются на необходимый вход,а затем на интересующую точку наблюдения за выводом.

этот процесс может быть реализован путем подключения зонда к наблюдательным узлам. напряжение узла и форма волны могут указывать на наличие ошибок в схеме принципов. Автоматически проверять все сигнальные соединения.

Как позволить производителям печатных плат уменьшить количество ошибок при проектировании печатных плат повысить эффективность проектирования

Давайте взглянем, чтобы обнаруженные узлы и напряжение были видны:

Итак, с помощью симуляции мы можем непосредственно наблюдать результаты и подтвердить правильность схемы печатной платы. Кроме того, можно исследовать изменения в конструкции путем тщательной настройки стимулирующих сигналов или значений компонентов.Поэтому моделирование схемы может сэкономить много времени для персонала, занимающегося разработкой и проверкой печатных плат, и увеличить возможность правильного проектирования.