(1) Thách đấu do thiết kế hệ thống điện tử

Với sự phức tạp và hệ thống thiết kế rộng lớn, các nhà thiết kế hệ thống điện đã được thiết kế các đường mạch trên 100MHZ, và tần số hoạt động của chiếc xe đã đạt đến hoặc vượt qua 50MHZ, và một số còn vượt hơn cả 100MHZ. Hiện tại, khoảng 50kg của các thiết kế có một tần số đồng hồ cao hơn 50MHz, và gần 20 Name của các thiết kế có một tần số đồng hồ cao hơn 120MHz.

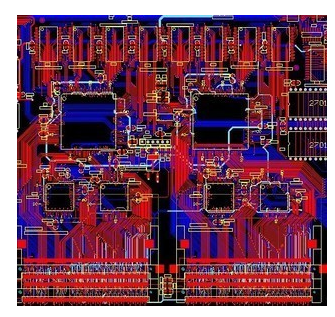

Khi hệ thống hoạt động ở 50MHz, sẽ có hiệu ứng đường truyền và vấn đề về độ trung tín hiệu; Khi đồng hồ hệ thống đến 120MHz, Trừ khi dùng kiến thức thiết kế mạch tốc độ cao, Mô- ti được thiết kế dựa trên phương pháp truyền thống sẽ không hoạt động. Do đó, PCB tốc độ cao Thiết kế đã trở thành một phương pháp thiết kế mà thiết kế hệ thống điện tử phải chọn. Tính cách điều khiển quá trình thiết kế chỉ có thể được thực hiện bằng cách sử dụng kỹ thuật thiết kế của các thiết kế mạch tốc độ cao..

(2) Hệ thống tốc độ cao

It is generally believed that if the tần số of a digital Logic mạch gan gan to or beyond 45.HZ~50MHZ, and the computer above this tần số has occupied a certain part of the electric system (for example, 1/3), it is called a high-speed mạch.

Trên thực tế, tần số điều hoà của mép tín hiệu còn cao hơn tần số của tín hiệu. Chính sự tăng lên và giảm các cạnh của tín hiệu (hay các cú nhảy tín hiệu) gây ra kết quả bất ngờ trong tín hiệu truyền tín hiệu. Do đó, thông thường sẽ đồng ý nếu khoảng thời gian truyền tải trên đường lớn hơn 1/2 so với thời gian khởi động tín hiệu điện tử, các tín hiệu đó được coi là tín hiệu tốc độ cao và tạo ra hiệu ứng đường truyền.

Tín hiệu phát tín hiệu xảy ra ngay khi trạng thái tín hiệu thay đổi, như thời gian bay lên hoặc rơi. Tín hiệu di chuyển một thời gian cố định từ lúc lái đến lúc nhận. Nếu thời gian truyền tín hiệu không bằng 1/2 của thời gian tăng hay rơi, tín hiệu phản chiếu từ đích nhận sẽ đến được đích trước khi tín hiệu thay đổi trạng thái. Ngược lại, tín hiệu phản chiếu sẽ đến được đích sau khi tín hiệu thay đổi trạng thái. Nếu tín hiệu phản chiếu mạnh, thì hình sóng trộn lại có thể thay đổi trạng thái logic.

(3) Xác định tín hiệu tốc độ cao

Phía trên chúng ta đã xác định những điều kiện để gây ra hiệu ứng đường truyền, Nhưng làm sao chúng ta biết được liệu sự chậm trễ có lớn hơn 1/2 thời gian phát tín hiệu kết thúc ổ đĩa? Thường, Thông thường giá trị của thời gian phát tín hiệu có thể được đưa ra trong tay thiết bị, và thời gian truyền tín hiệu được xác định bởi độ dài đường dây thật sự trong... Thiết kế PCB. Correspondence between signal rise time and allowable wiring length (delay).

Sự chậm trễ trên máy tính là 0.167ns. Tuy nhiên, nếu có nhiều cầu, nhiều chốt thiết bị, và nhiều hạn chế được thiết lập trên cáp, sự chậm trễ sẽ tăng lên. Thông thường, thời gian phát tín hiệu của các thiết bị logic tốc độ cao khoảng 0.2. Nếu có các thẻ Gaas trên bảng, thì độ dài dây tối đa là 7.6mm.

Hãy để Tr là thời gian phát tín hiệu và TPD là thời gian báo hiệu phóng nhanh. Nếu T569;1371;1654TPD., Tín hiệu rơi ở một nơi an toàn.. Nếu 2T55536;137555536;T5536;137; 165; 4TPD, Tín hiệu sẽ rơi xuống vùng không chắc chắn. Nếu T5226; 137; 164; 2TPD, Tín hiệu sẽ rơi ở khu vực vấn đề.. Tín hiệu rơi xuống vùng không xác định và khu vực khó khăn, high-speed Dây dẫn PCB methods should be used.