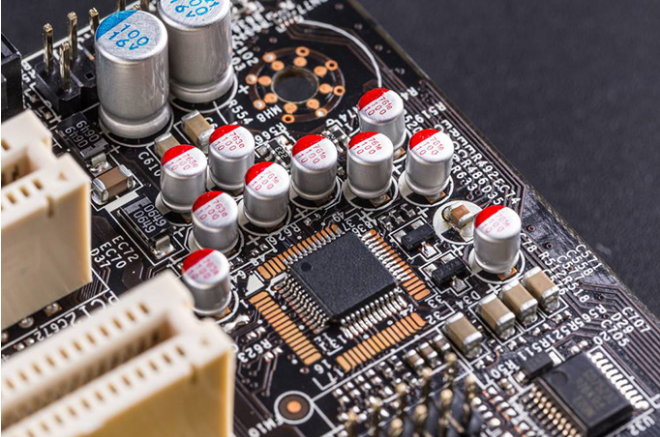

Đối với các nhà sản xuất PCB, thiết kế tương thích điện từ chắc chắn là một trọng tâm trong quá trình thiết kế bảng mạch. Bài viết này sẽ thảo luận về cách cải thiện khả năng tương thích điện từ theo hai cách.

1. Giới thiệu

Nhiều vấn đề về độ tin cậy và ổn định của thiết bị điện tử là do sự thất bại trong thiết kế tương thích điện từ. Các vấn đề thường gặp bao gồm biến dạng tín hiệu, tiếng ồn tín hiệu quá lớn, tín hiệu không ổn định khi làm việc, sự cố hệ thống, hệ thống dễ bị nhiễu môi trường, khả năng chống nhiễu kém. Thiết kế tương thích điện từ là một kỹ thuật rất phức tạp, từ thiết kế đến kiến thức về điện từ và nhiều hơn nữa. Bài viết này thảo luận về một số mẹo thực nghiệm về thiết kế lớp và bố trí lớp để cung cấp một số tài liệu tham khảo cho các kỹ sư điện tử.

Thứ hai, cấu hình số tầng

Số lượng các lớp của bảng mạch PCB chủ yếu bao gồm các lớp điện, hình thành và các lớp tín hiệu, và số lượng các lớp là tổng của mỗi lớp. Trong quá trình thiết kế, bước đầu tiên là phối hợp và phân loại tất cả các nguồn và mặt đất cũng như các tín hiệu khác nhau và triển khai và thiết kế trên cơ sở phân loại. Nói chung, các nguồn điện khác nhau nên được chia thành các lớp khác nhau và các mặt đất khác nhau nên có mặt phẳng mặt đất tương ứng. Các tín hiệu đặc biệt khác nhau, chẳng hạn như tín hiệu đồng hồ và tần số cao, cần được thiết kế riêng biệt và cần thêm mặt phẳng nối đất để che chắn các tín hiệu đặc biệt để cải thiện khả năng tương thích điện từ. Khi chi phí cũng là một trong những yếu tố cần xem xét, cần tìm sự cân bằng giữa khả năng tương thích điện từ và chi phí của hệ thống trong quá trình thiết kế.

Cân nhắc đầu tiên trong thiết kế lớp điện là loại và số lượng nguồn cung cấp. Nếu chỉ có một nguồn điện, bạn có thể xem xét sử dụng một lớp điện duy nhất. Trong trường hợp yêu cầu công suất cao, cũng có thể có nhiều lớp công suất để cung cấp năng lượng cho các thiết bị ở các lớp khác nhau. Nếu có nhiều nguồn điện, hãy xem xét thiết kế nhiều lớp điện hoặc chia các nguồn điện khác nhau trên cùng một lớp. Tiền đề của sự phân chia là không có sự giao thoa giữa các nguồn điện. Nếu có một chéo, nhiều lớp điện phải được thiết kế.

Các lớp tín hiệu nên được thiết kế để xem xét các đặc tính của tất cả các tín hiệu. Phân lớp và che chắn các tín hiệu đặc biệt là một ưu tiên. Thông thường, thiết kế đầu tiên được thực hiện với phần mềm thiết kế và sau đó được sửa đổi theo các chi tiết cụ thể. Mật độ tín hiệu và tính toàn vẹn của tín hiệu đặc biệt phải được xem xét trong thiết kế lớp. Đối với thông tin đặc biệt, hệ thống phải được thiết kế như một lớp che chắn khi cần thiết.

Trong trường hợp bình thường, thiết kế veneer hoặc đôi không được khuyến khích trừ khi chi phí hoàn toàn được xem xét. Mặc dù việc xử lý veneer và đôi rất đơn giản và hiệu quả về chi phí, trong trường hợp mật độ tín hiệu cao và cấu trúc tín hiệu phức tạp, chẳng hạn như mạch kỹ thuật số tốc độ cao hoặc mạch lai analog-digital, veneer không có hệ thống tham chiếu chuyên dụng, cho phép tăng diện tích vòng lặp và tăng bức xạ. Khả năng chống nhiễu của hệ thống cũng giảm do thiếu lớp che chắn hiệu quả.

Thứ ba, thiết kế bố trí lớp PCB

Sau khi xác định các tín hiệu và lớp, bố cục của mỗi lớp cũng cần được thiết kế một cách khoa học. Thiết kế bố trí của lớp giữa của thiết kế bảng PCB tuân theo các nguyên tắc sau:

(1) Đặt mặt phẳng nguồn điện liền kề với mặt phẳng mặt đất tương ứng. Mục đích của thiết kế này là tạo thành một tụ điện ghép nối và làm việc với tụ điện tách rời trên PCB để giảm trở kháng của mặt phẳng công suất trong khi đạt được hiệu ứng lọc rộng hơn.

b) Lựa chọn lớp tham chiếu là rất quan trọng. Về mặt lý thuyết, các tầng công suất và mặt phẳng cơ sở có thể được sử dụng làm lớp tham chiếu, nhưng các tầng hình thành thường có thể được nối đất, do đó hiệu ứng che chắn tốt hơn nhiều so với các tầng công suất, vì vậy nói chung, mặt phẳng mặt đất được ưu tiên làm mặt phẳng tham chiếu.

(3) Các tín hiệu quan trọng từ hai lớp liền kề không thể vượt qua phân vùng. Nếu không, một vòng lặp tín hiệu lớn hơn sẽ được hình thành, dẫn đến bức xạ và khớp nối mạnh hơn.

(4) Để duy trì tính toàn vẹn của mặt phẳng nối đất, không thể định tuyến trên mặt phẳng nối đất. Nếu mật độ dây tín hiệu quá lớn, bạn có thể xem xét định tuyến ở các cạnh của mặt phẳng nguồn.

(5) Thiết kế hình thành bên dưới tín hiệu quan trọng như tín hiệu tốc độ cao, tín hiệu thử nghiệm, tín hiệu tần số cao, v.v., làm cho đường đi của vòng tín hiệu ngắn nhất và bức xạ tối thiểu.

(6) Trong quá trình thiết kế mạch tốc độ cao, phải xem xét cách xử lý bức xạ của nguồn điện và nhiễu cho toàn bộ hệ thống. Nói chung, diện tích của mặt phẳng nguồn điện phải nhỏ hơn diện tích của mặt phẳng mặt đất để mặt phẳng mặt đất có thể che chắn nguồn điện. Thông thường, mặt phẳng nguồn cần thụt gấp 2 lần độ dày của môi trường thay vì mặt đất. Nếu bạn muốn giảm độ lõm của lớp công suất, độ dày của phương tiện phải càng nhỏ càng tốt.

Nhiều lớp PCB bố trí thiết kế nên tuân theo các nguyên tắc chung:

(1) Mặt phẳng nguồn phải gần mặt phẳng nối đất và được thiết kế bên dưới mặt phẳng nối đất.

(2) Các lớp dây phải được thiết kế để tiếp giáp với toàn bộ mặt phẳng kim loại.

(3) Tín hiệu kỹ thuật số và tín hiệu analog phải được thiết kế để tách biệt. Đầu tiên, tránh tín hiệu kỹ thuật số và tín hiệu analog trên cùng một lớp. Nếu không thể tránh khỏi, hệ thống dây điện khu vực có thể được phân chia bằng tín hiệu tương tự và kỹ thuật số và các khe cắm được sử dụng để phân chia khu vực tín hiệu tương tự. Cô lập với khu vực tín hiệu kỹ thuật số. Tương tự với nguồn analog và digital. Đặc biệt, bức xạ từ các nguồn điện kỹ thuật số rất lớn, vì vậy chúng phải được cách ly và che chắn.

(4) Các đường in trong lớp giữa tạo thành ống dẫn sóng phẳng và các đường vi băng được hình thành trong lớp bề mặt. Đặc tính truyền tải của hai loại khác nhau.

(5) Mạch đồng hồ và mạch tần số cao là nguồn gây nhiễu và bức xạ chính. Chúng phải được sắp xếp riêng biệt và tránh xa các mạch nhạy cảm.

(6) Dòng điện đi lạc và dòng bức xạ tần số cao chứa trong các lớp khác nhau là khác nhau, không thể được đối xử như nhau khi định tuyến.

Khả năng tương thích điện từ của PCB có thể được cải thiện đáng kể thông qua thiết kế nhiều lớp và bố trí nhiều lớp.

Thiết kế số tầng chủ yếu xem xét các lớp năng lượng và địa tầng, tín hiệu tần số cao, tín hiệu đặc biệt và tín hiệu nhạy cảm.

Bố trí lớp chủ yếu xem xét các bố trí ghép nối, nối đất và đường dây điện khác nhau, bố trí tín hiệu đồng hồ và tốc độ cao, tín hiệu tương tự và bố trí thông tin kỹ thuật số.