Nowadays, CMOS Technology make FPGA/О - интерфейсs. одновременно, in recent years, низкое энергопотребление стало основной концепцией/O interfaces. самый эффективный способ снижения энергопотребления - снизить напряжение, and the voltage reduction will result in a smaller noise margin allowed by the I/O interface. поэтому, it is very necessary for FPGA users to quantify the system-level synchronous switching noise (SSN) in the chip, посылка, and PCB environment.

в данной статье систематически описывается SSN, и основное внимание уделяется буферу вывода FPGA, вызванному SSN. этот шум обычно называется шумом синхронного переключателя (SSO), который отличается от SSN, вызываемого буфером ввода. была представлена информация о причинах, связанных с одноточечным входом в систему, и был предложен поэтапный подход к моделированию входа в систему. В то же время в настоящем документе разъясняется, как модель SSO соотносится с частотными и временными измерениями, и предлагаются несколько методов проектирования PCB для уменьшения SSO.

The formation mechanism of system-level SSO

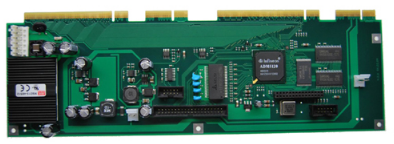

A PCB with FPGA is a complex system that can be divided into a chip part containing active circuits, встроенные пассивные элементы со поддерживающими линиями, and a circuit board part that provides connections between the FPGA and the outside. в такой системе, it is difficult to understand the noise characteristics inside the chip. Therefore, it is very valuable to quantify the SSO at the near and far ends of the След PCB соединение с FPGA. There are two main factors that cause SSO: the impedance of the power distribution network (PDN) and the mutual inductance coupling between the switch I/O.

с точки зрения системы, PDN includes wafer-level, класс упаковки, and board-level components, Они совместно снабжают сеть CMOS. When a certain number of CMOS output drive circuits are turned on at the same time, большой ток мгновенно вливает в индуктивный элемент PDN, приводить к понижению напряжения дельта - I. Interconnect structures generate parasitic inductances, например, шаровой сетчатый массив герметизирован электрическим припоем шариков и PCB - перерывом в питании. This rapidly changing current also excites radial electromagnetic waves between the power/лицом к лицу. The electromagnetic waves are reflected from the planar edge of the PCB, звучать между силами/ground plane, создавать колебание напряжения.

Еще одной важной причиной для SSO является взаимная индуктивная связь, особенно в том, что касается упаковки чипов / PCB по краям. на чипе BGA запечатаны сварные шарики и сквозные отверстия на PCB, принадлежащие к многолинейной структуре, тесно связанной между собой. каждый сварной шар I / O и соответствующее ему отверстие PCB для прохода и его ближайшая заземленная сфера и заземленное отверстие образуют замкнутое кольцо. при изменении состояния нескольких портов I / O эти сигнальные цепи протекают через переходный I / O ток. этот переходный ток ввода / вывода создаёт магнитное поле, проникая в соседний сигнальный контур и генерируя шумы индуктивного напряжения.

An excellent SSO model should be able to reflect the basic formation mechanism of SSO. модель для прогнозирования иерархии SSO в PCB. At the chip level, Нам нужна модель буфера вывода, которая может обеспечивать Точное распределение тока по линиям питания и сигналам при ограниченной сложности. At the packaging level, Для простоты, modeling tools can be used to obtain the PDN model and the signal coupling model, Однако взаимодействие между PDN и моделями связи сигналов следует тщательно продумать. These two models act as a bridge, модель буфера вывода, связывающая кристалл с закреплённым выступом, и модель уровня PCB для сварных шаров. The PDN model of the PCB usually includes the power/уровень земли и большая емкость/decoupling capacitors on it, модель связи сигналов системы PCB включая a tightly coupled via array and loosely coupled signal traces on different signal layers. взаимодействие между этими двумя моделями уровня PCB проявляется в сетке отверстий PCB. It is from here that inductive crosstalk brings noise into the PDN model, и шум delta - I в свою очередь снижает качество I/O signal. Этот метод послойного моделирования разумно сохраняет имитационную точность, and at the same time improves the computational efficiency of such complex systems.