30分以内の返信、1時間のエンジニアリング対応、24時間の技術サポート、顧客の待ち時間の節約、あらゆる面での製品開発と生産サイクルの短縮、製品の発売時間の節約、製品の市場での迅速な占有。

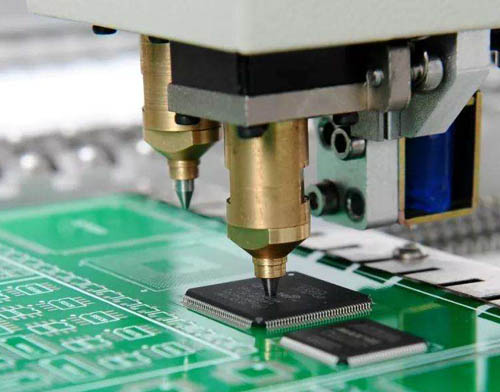

10年以上の開発で、技術と容量を追加するために年々成長しています。標準PCBからRF回路、マイクロ波回路基板、多層PCB、リジッドフレキシブルPCB、HDI PCB、IC基板、ICテストボード、PCBAまでのPCB技術組み立て。

私たちのパートナーのサポートと信頼は私たちの進歩の原動力です。 私たちは、お客様との双方にメリットのあるビジネスを探しています。 私たちの企業文化には、大小の顧客は存在しません。 常に優れたサービスを提供するために最善を尽くすことは私たちの目標です。

Isola、Panasonic、TUC、ITEQ、Shengyi、KB、Rogers、Arlon、Taconic、Doosan、Mitsubishi Gas、DuPontなどのPCB材料サプライヤーの幅広い選択

ストック材料:FR408、370HR、TU872、RO4350B、RO4003C、RT5880、RO3010、RO3003、RF35、TLY-5、Megtron4、Megtron6、S1000-2、IT180、F4BMPCBプロトタイプ材料。

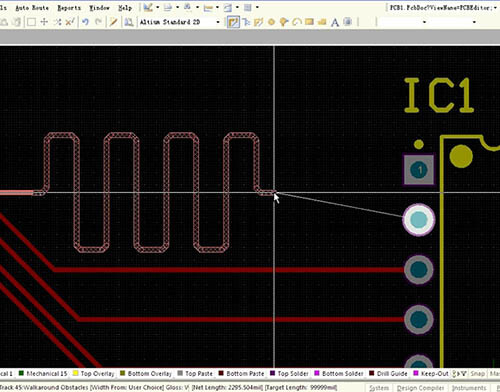

FR-4 PCB、多層回路基板、HDI PCB、セラミックPCB、PTFEプリント回路基板、ハイブリッド回路、テフロンPCB、RF PCB、ロジャースPCBをサポートします。 高度なPCBERP追跡管理システムは、納期で業界をリードしており、PCBオンタイム納期は95%を超えています。

厳格な品質管理システムにより、10年以上にわたって中国で最も経験豊富なプリント回路基板メーカーの1つが保証されました。 iPCBプロフェッショナルファブリケーションPCBプロトタイプのPCBファクトリー、IPCクラスIII規格は、お客様の要件に基づいて選択できます。

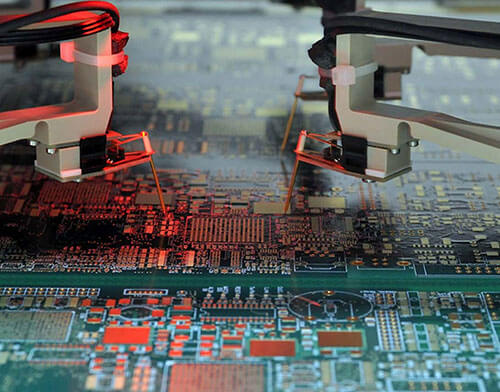

iPCBは、世界中の10,000以上のハイテク研究開発、製造、およびサービス企業と継続的に協力してきました。 その製品は、通信回路、産業用制御回路基板、鉄道輸送PCBボード、医療用電子機器PCB、コンピューターPCB、半導体基板、自動車用電子機器PCB、およびその他のプリント回路基板の分野で使用されています。 iPCBは、世界60か国以上をカバーするリソースを備えたワンストップPCB-PCBAアセンブリ製造も提供しています。

電子機器の保護:iPCBのアクリルコンフォルムコーティングサービス

2025-02-25

2021-12-13

RO 4350 BとFR 4は低コスト高周波PCBを製造する

2023-02-24